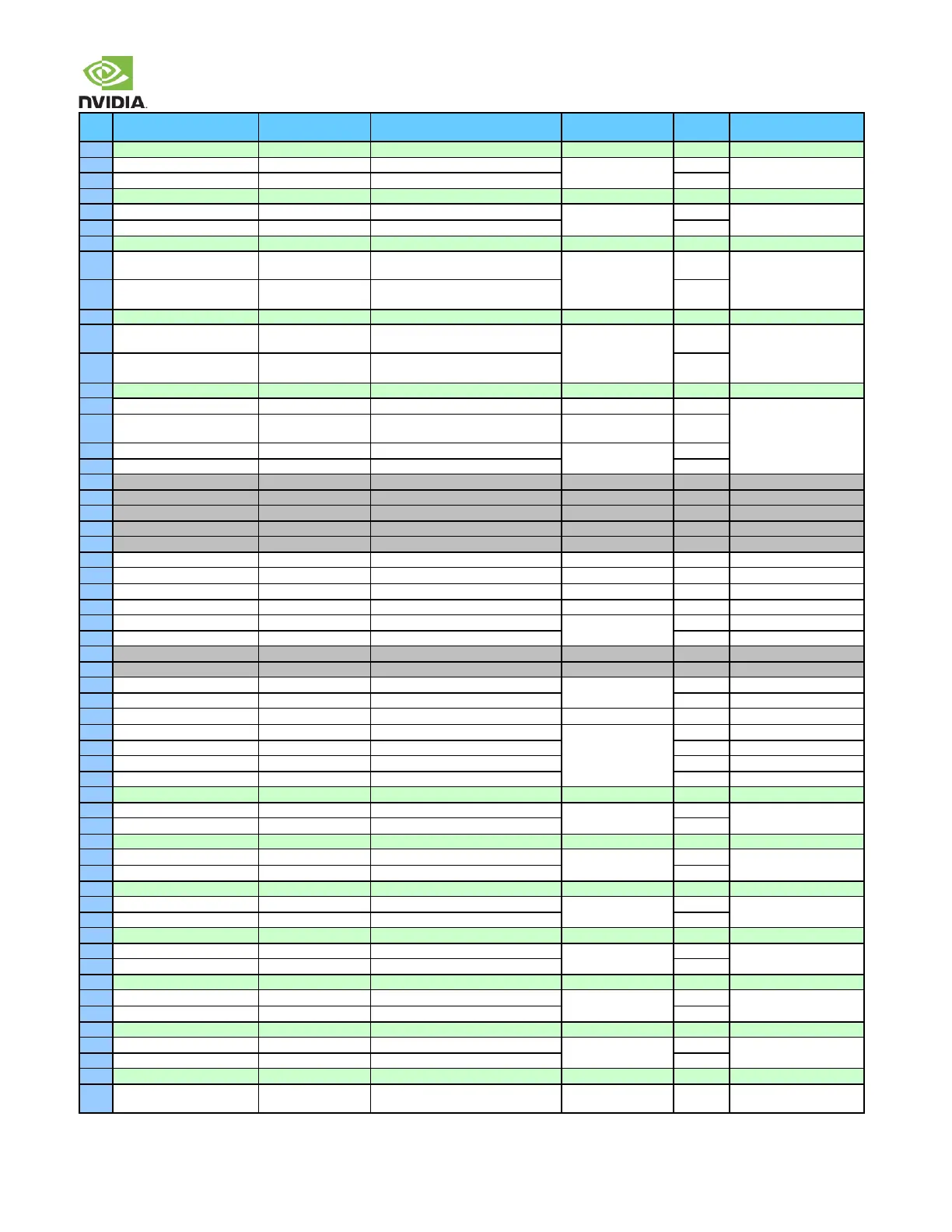

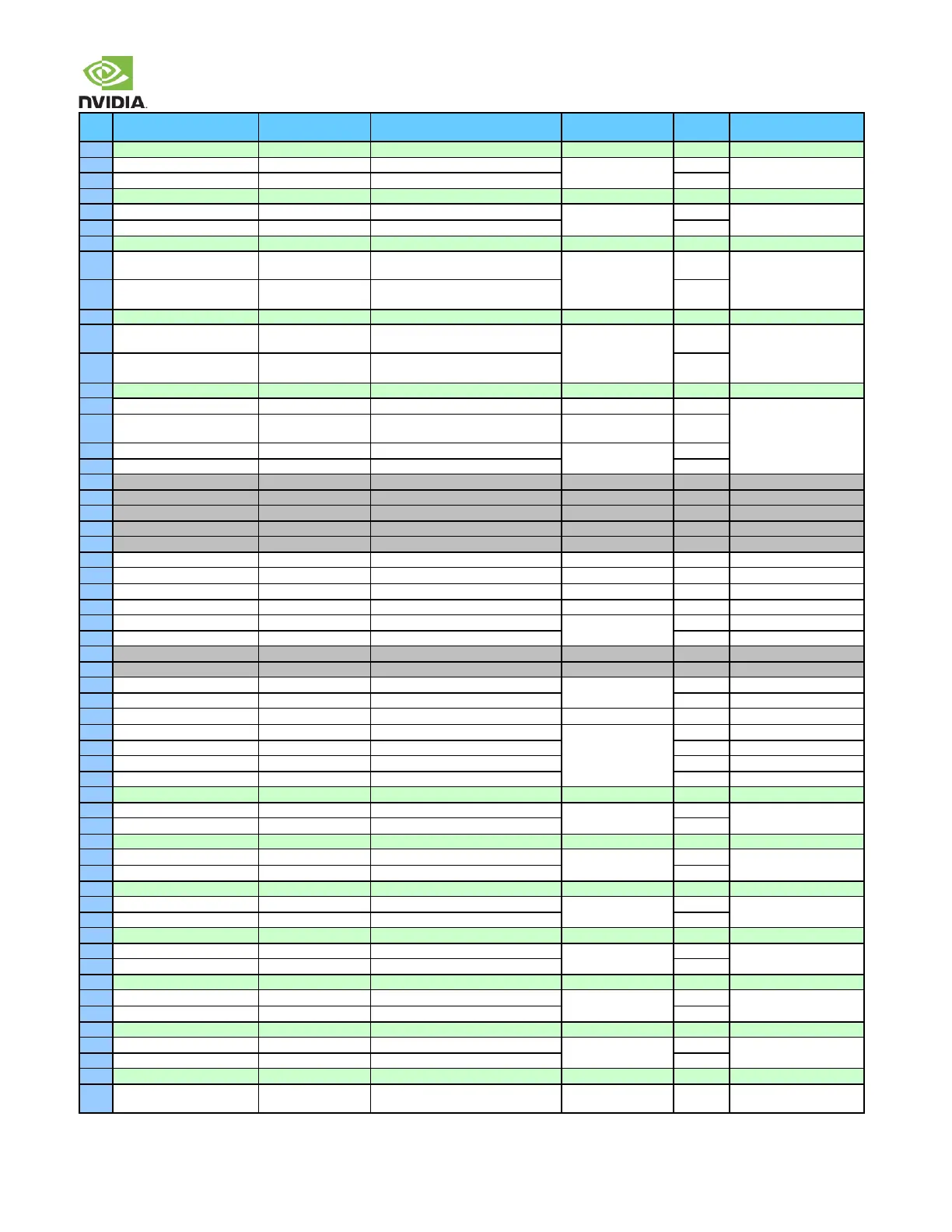

NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 98

Usage on the Carrier

Board

DisplayPort 1 Lane 1 or HDMI Lane 1

AC-Coupled on carrier

board

DisplayPort 1 Lane 1+ or HDMI Lane 1+

PCIe 2 Transmit+ (PCIe IF #0 Lane 2 or

PCIe IF #1 Lane 0)

PCIe PHY, AC-Coupled on

carrier board

PCIe 2 Transmit (PCIe IF #0 Lane 2 or

PCIe IF #1 Lane 0)

USB SS 0 Transmit+ (USB 3.0 Port #0

muxed w/PCIe #2 Lane 0)

USB SS PHY, AC-Coupled on

carrier board

USB SS 0 Transmit (USB 3.0 Port #0

muxed w/PCIe #2 Lane 0)

PCIE 2 Clock Request (PCIe IF #1)

Open Drain 3.3V, Pull-up on

the module

PCIE 1 Clock Request (mux option - PCIe

IF #2)

PCIE 0 Clock Request (PCIe IF #0)

PCIe 0 Reset (PCIe IF #0)

Camera Flash Enable or GPIO

I2S Audio Port 1 Left/Right Clock

I2S Audio Port 1 Data Out

DisplayPort 1 Lane 2 or HDMI Lane 0

AC-Coupled on carrier

board

DisplayPort 1 Lane 2+ or HDMI Lane 0+

PCIe RFU Transmit+ (PCIe IF #0 Lane 3 or

USB 3.0 Port #1)

PCIe PHY, AC-Coupled on

carrier board

Loading...

Loading...