Safety Manual for MPC5777M, Rev. 1.1

Address decoding coverage

NXP Semiconductors64

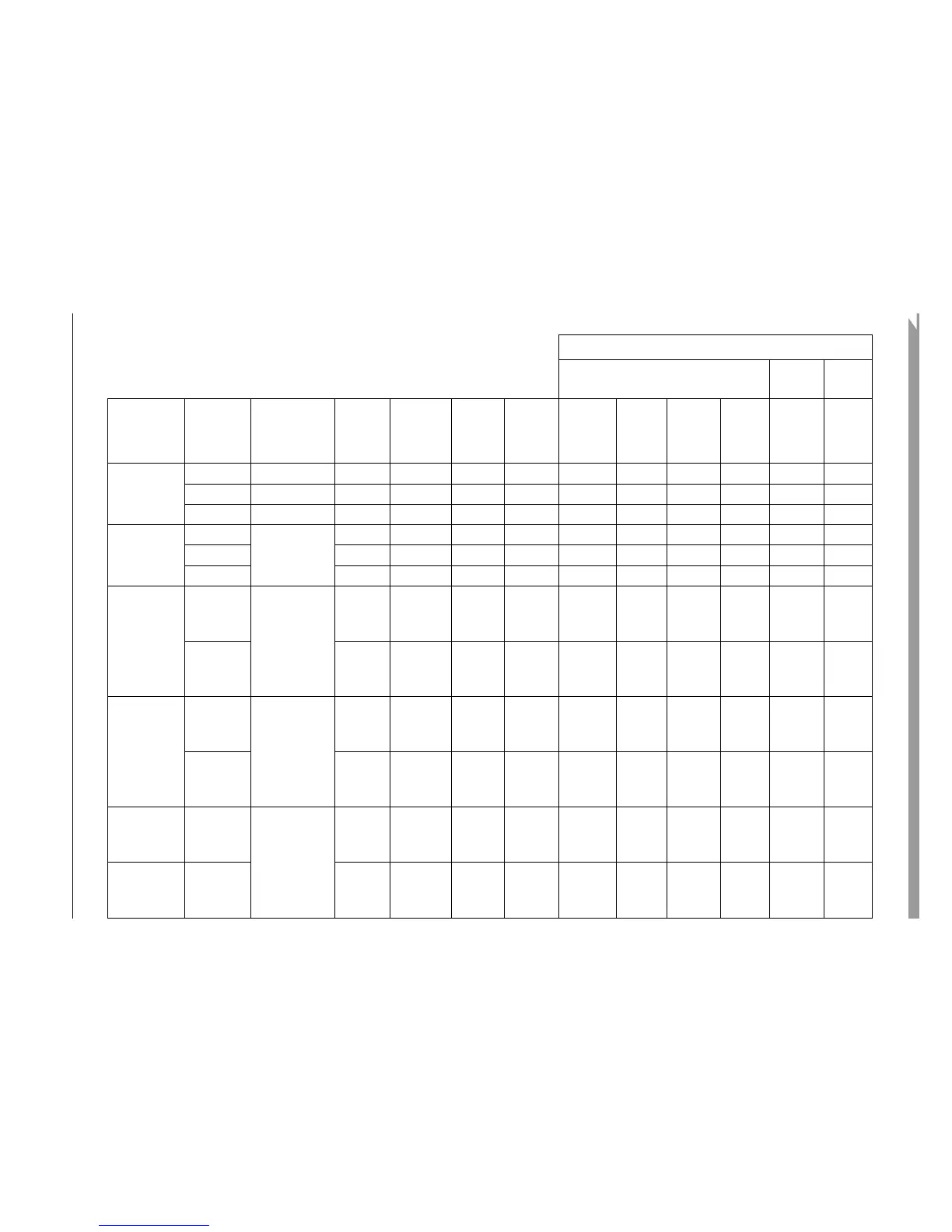

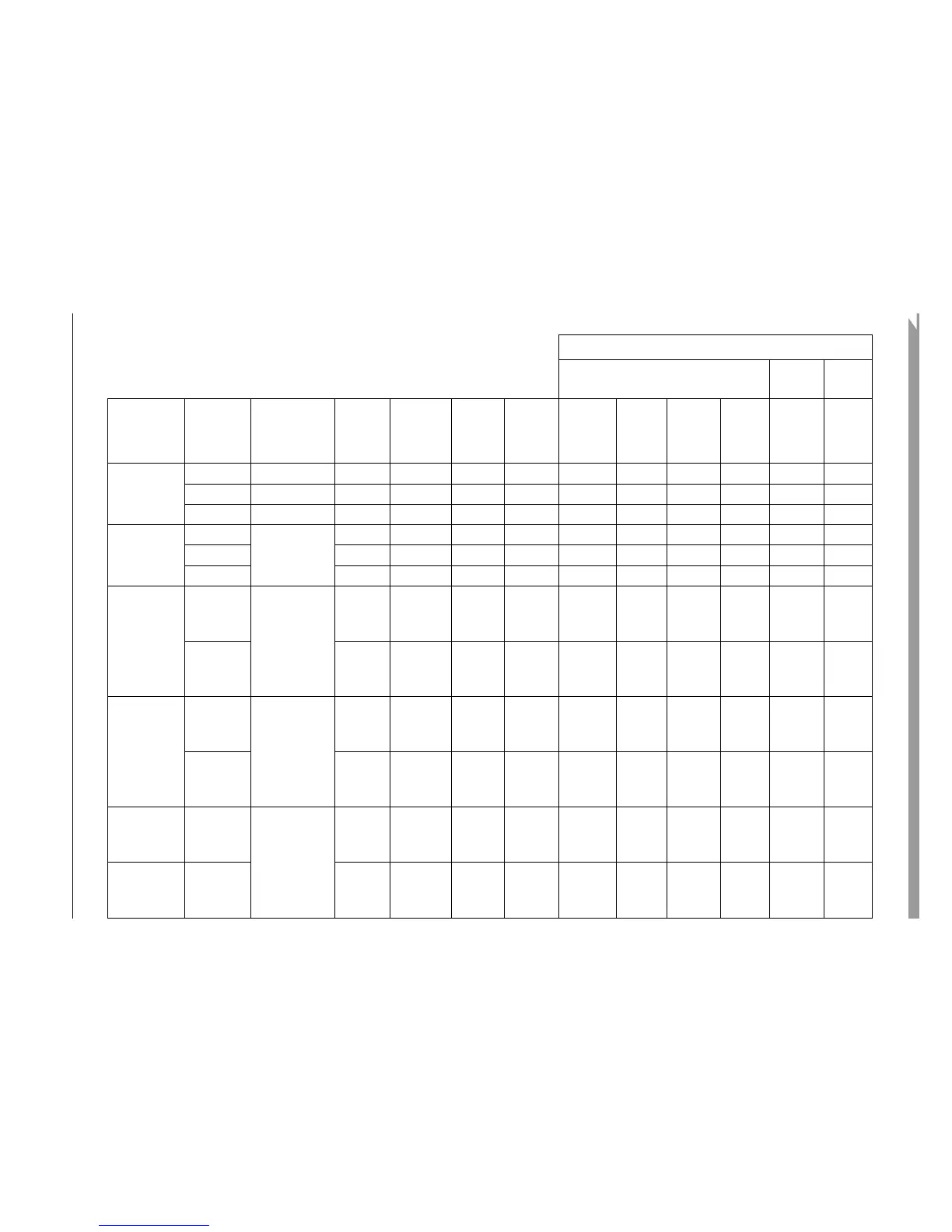

Table 4. Address decoding

Word address predecoding bits

Row selection

Column

selection

Location Memory

Shall be

tested?

Mux

Number of

words

Bits

per

word

Number

of

address

bits

Dec D Dec C Dec B Dec A Dec E

Block

address

Core_0

(Safety Core)

I-Mem yes 8 2048 72 13 — A<12> A<11:9> A<8:6> A<5:3> A<2:0>

D-Mem0

1

yes 8 8192 40 13 — A<12> A<11:9> A<8:6> A<5:3> A<2:0>

D-Mem1

1

yes 8 8192 40 13 — A<12> A<11:9> A<8:6> A<5:3> A<2:0>

Core_1

I-Mem not mandatory

application

dependent

8 2048 72 13 — A<12> A<11:9> A<8:6> A<5:3> A<2:0>

D-Mem0

1

8 8192 40 13 — A<12> A<11:9> A<8:6> A<5:3> A<2:0>

D-Mem1

1

8 8192 40 13 — A<12> A<11:9> A<8:6> A<5:3> A<2:0>

FlexRay0

DRAM

not mandatory

application

dependent

4 128 26 10 — A<9:7> A<6:4> A<3:2> A<1:0> —

LRAM1,2 4 96 63 10 — A<9:7> A<6:4> A<3:2> A<1:0> —

FlexRay1

DRAM

not mandatory

application

dependent

4 128 26 10 — A<9:7> A<6:4> A<3:2> A<1:0> —

LRAM1,2 4 96 63 10 — A<9:7> A<6:4> A<3:2> A<1:0> —

TTCAN TTCAN

not mandatory

application

dependent

16 5120 39 13 A<12:10> A<9:8> A<7:6> A<5:4> A<3:0> —

NAR NAR1...4 4 64 128 12 — A<11> A<10:8> A<7:5> A<4:3> A<2:0>

Loading...

Loading...