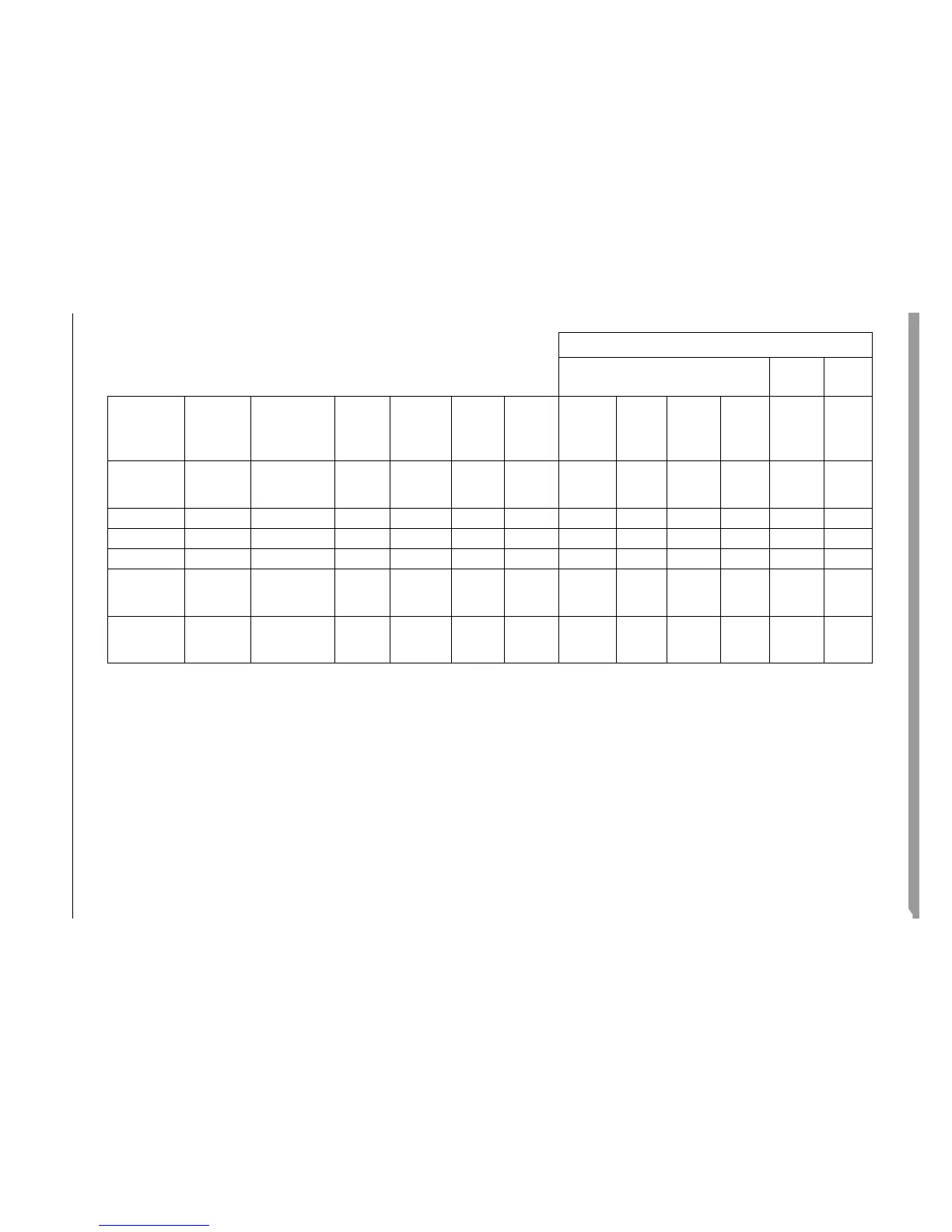

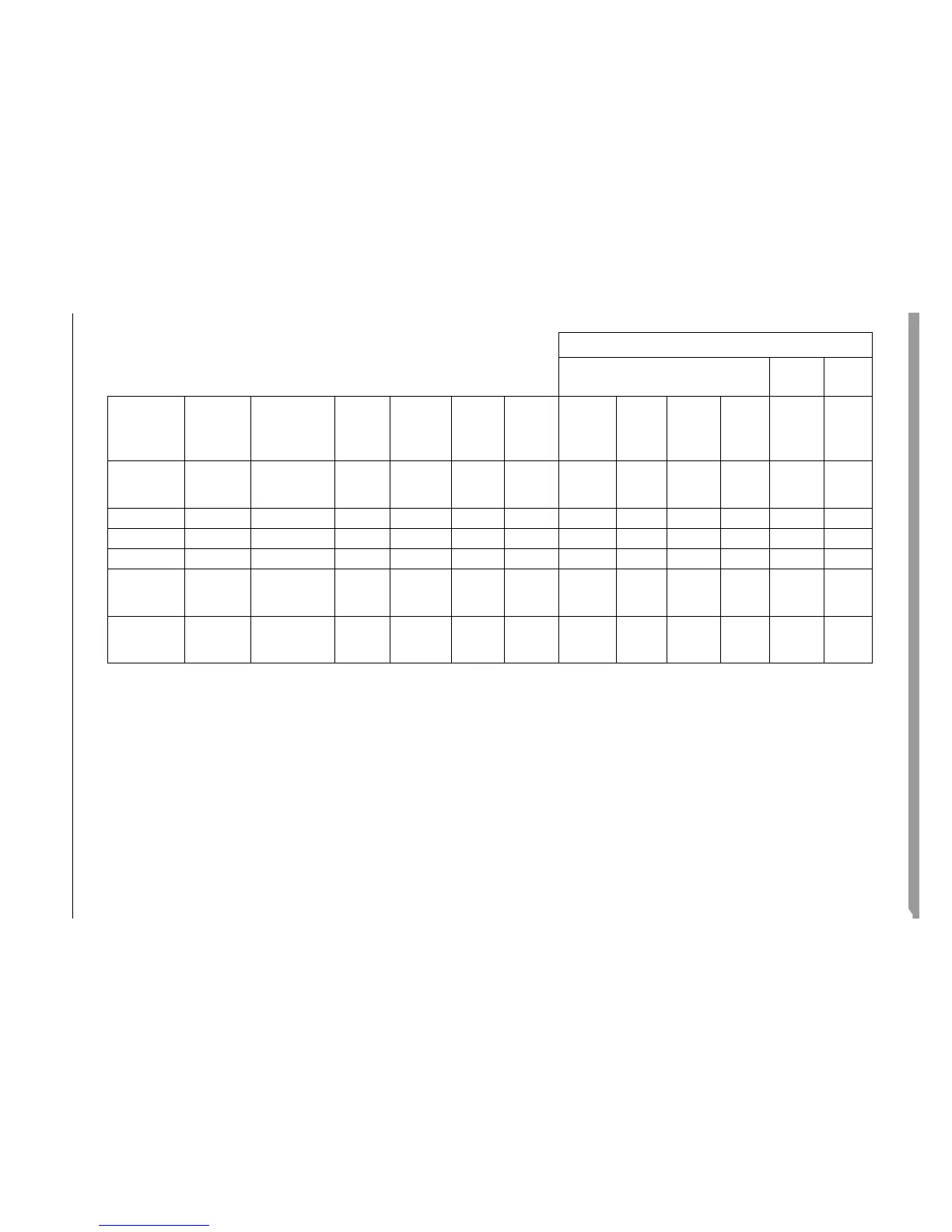

Address decoding coverage

Safety Manual for MPC5777M, Rev. 1.1

NXP Semiconductors 65

Platform DMA0,1

not mandatory

application

dependent

4 256 72 10

—

A<9:7> A<6:4> A<3:2> A<1:0> —

Platform Overlay1,2 yes 4 1024 72 12 — A<11> A<10:8> A<7:5> A<4:3> A<2:0>

Platform SRAM1...6 yes 16 8192 72 13 A<12:10> A<9:8> A<7:6> A<5:4> A<3:0> —

Platform SRAM7 yes 16 2560 72 13 A<12:10> A<9:8> A<7:6> A<5:4> A<3:0> —

Platform FEC/FICO

not mandatory

application

dependent

4 128 44 10 — A<9:7> A<6:4> A<3:2> A<1:0> —

Platform FEC/MIB

not mandatory

application

dependent

4 64 40 10 — A<9:7> A<6:4> A<3:2> A<1:0> —

Table 4. Address decoding (continued)

Word address predecoding bits

Row selection

Column

selection

Location Memory

Shall be

tested?

Mux

Number of

words

Bits

per

word

Number

of

address

bits

Dec D Dec C Dec B Dec A Dec E

Block

address

Loading...

Loading...