Note:

-RST

and

-A

TN

are

shown

de-asserted

(high)

Note:

(Ack,nowleage)

-ACK

'(Attention)

-ATN

(Message)

-MSG

(Reset)

-AST

(Data b

it)

DB

(7-0.

P)

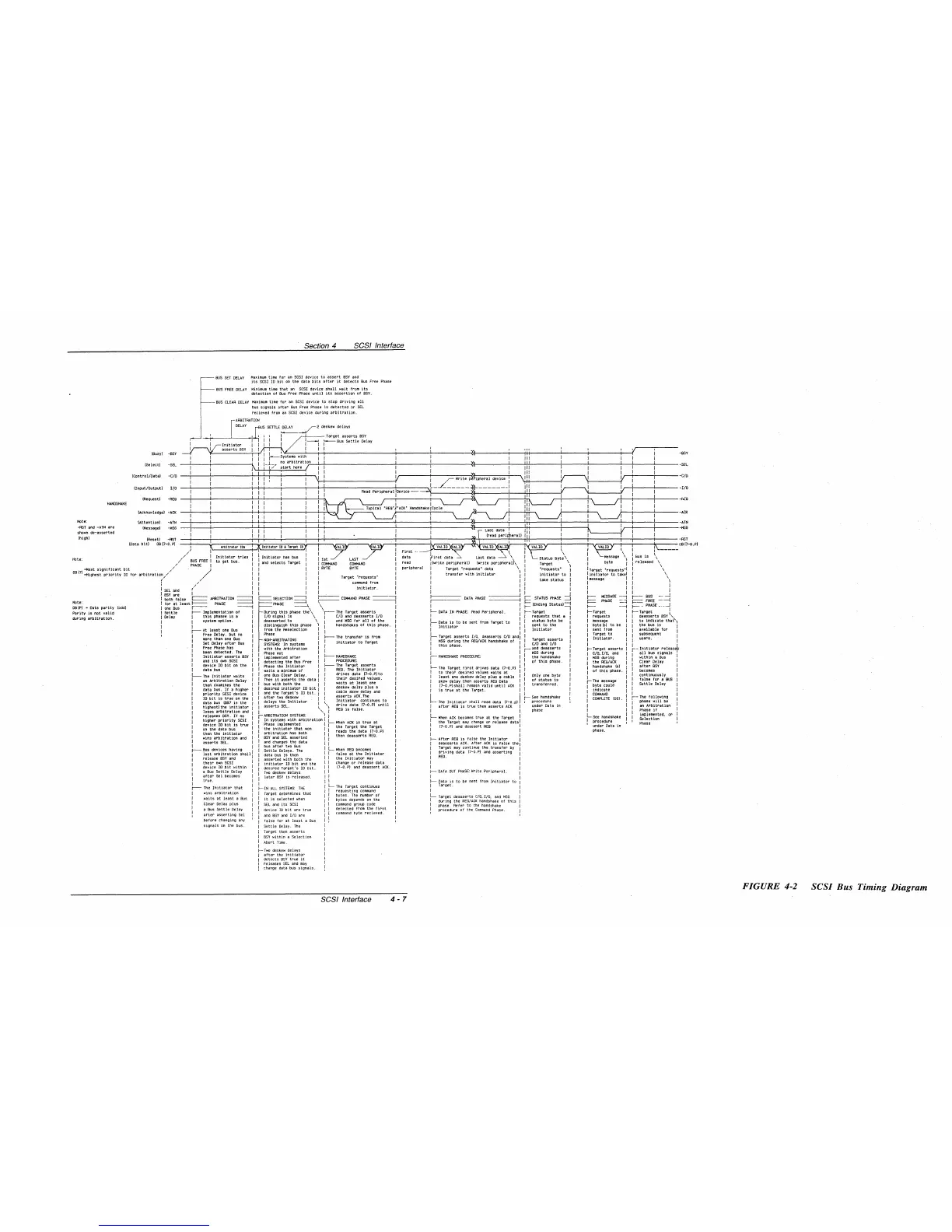

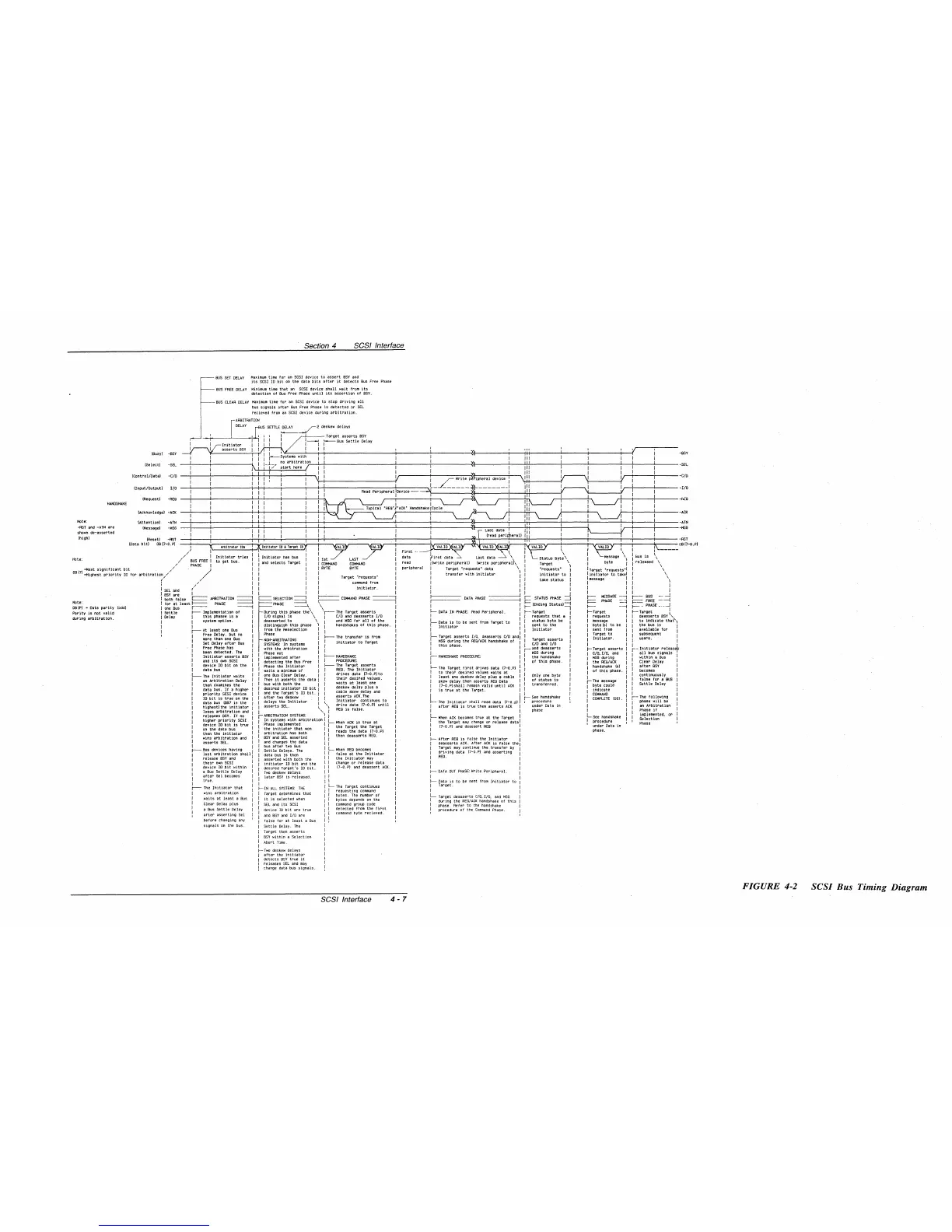

Section 4

SCSI Interface

BUS

SET

DELAY

Maximum

time

for

an

SCSI

device

to

assert

BSY

ana

its

SCSI

ID

bit

on

the

data

bits

after

it

aetects

Bus

Free Phase

BUS

FREE

DELAY

Minimum

time

that

an

SCSI

device

shall

wait

from

its

detection

of

Bus

Free Phase

until

its

assertion

of

BSY,

BUS

CLEAR

DELAY

Maximum

time

for

an

SCSI

device

to

stop

driving

all

bus

signals

after

Bus

Free

Phase

is

detected

or

SEL

recieved

from

an

SCSI

aevice

during

arbitration.

,

ARBITRATION

DELAY

i

BUS

SETTLE

~~2

deskew

delays

,---<_...,....-----'-

______

+'

~I

" I

Target

asserts

BSY

,

",

,----'

'---

Bus

Settle

Delay

,

",

" ,

, , "

-BSY

,.....----------r-1"',

l--~ystems

with ,

i 1

no

arbi

trati°rn_J-+-

___________________

~-------__i_I----------~~~<~----.,.......-_!_----~~---------t--------l----------.J---!-----l--------

-SEL

,-

,'7

~tart

here

( "

,i

I

, , ,

~)

---T-----.....JI.......-----------'---!-l-,-T-,--I-------l----.\'

'V

" r Write

pi?iPheral

device

,

, '

'1-,

-+-------------------r

, ...L

__

'

I I

Read

periPheral!Device-~-

------t-------!

---r----~----------~_7~----~----~--_+~

r--~--_+~

r--t------;.------

-C/O

r--+-------I--------

-1/0

r+--_+-----+-------

-h~G

)---t-----I.------.,-

-ACK

---+--~~----------4~_+---r------_+---I.-+------------------~---------T_----------(~---------T---I.Tr-------f------+---------~--_r-----7-------

ATN

,.......-+-------j--------MSG

---r-----+------------T-T-r---~------_T--_T_r--------------------~----------~----------~~~----~~~----r.+---------t------~;---------;_~r_----~-------RST

---+~~~~--~----~~~~~~_=~~~~--_;----'r.~~r------~~~--_r----------~~~~/~~/--~~

r.~~'r~~--_;'r~~'r--~--------T_~~~~_T--_r------~------~B(7-0.PI

/

),

,

InitIator

JO

, Target

JO

, " ALI

(,

,i

_____

_

/

,

I

't'

t

t·"

First

-- k

,

'

rst

data'

Last

data

,\',

" ,

"us

l'S

\,

,

nl

la

or

rles

,

Initiator

has

bUS,

,

1st

data

r

~

~

Status

byte',

, "

//

~~~s~AEE:

to

get

bus,

, and

selects

Target,

,

COMMAND

read,

(write

peripheral)

(write

periPheralr,

Target

\'

,

,released

\

~Most

significant

bit

//

/ ' , ,

BYTE

peripheral,

Target

"requests"

data

,

"requests",

'Target

"requests"'

, \

DB

(7)

-Highest

priority

10

for

arbitratton//

" , ,

transfer

with

initiator

)

initiator

to

,

'initiator

to

take'

, ,

(/

,

"Target

"requests",

"

take

status'

' message , ,

\\

r / , "

command

from'

" , ,

,/

, "

initiator.'

:",

, :

,

~~~

:~~

, , , " ,

""

, ...J

,

both

false

c:=::::=

ARBITRATION

-"I

c==

SELECTION

3 t===

COMMAND

PHASE

===~

:

DATA

PHASE

i r

STATUS

PHASE

=:J

E

=~~~~GE

3

r--

~~~E

=--1

,

for

at

least

~

PHASE

~

PHASE

---\

, , ,

~

(Ending

Status)=={

r--

---1

~

PHASE

___

-I

:

~~~t~~S

r--

Implementation

of

, During

this

phase

the\

\.-

The

Target

asserts

~

DATA

IN

PHASE:

R.ad

Peripheral.

'

~

Target

,I-Target

,

I--

Target

t

, Delay

,thiS

phasee

is

a , I/O

signal

is

"C/O

and

deasserts

I/O'

:'

requests

that

a,

'requests

"deasserts

BSY

,

,

,system

option.

,deasserted

to

\,

and

MSG

for

all

of

the

',

__

Data

is

to

be

sent

from Target

to

"

status

byte

be,

'message

, ,

to

indicate

that\

I'

,

distinguish

this

phase

),

handshakes

of

this

phase.

I

Initiator

"

sent

to

the

,

,byte

(s)

to

be , ,

the

bus

is

,

I

r--

At

least

one

Bus

,

pfrhoamsethe

Reselection

'"

,Initiator

,

,sent

from

"available

for

,

,

,Free

Delay

but

no

,

I--

L,

Target

asserts

1/0.

deasserts

C/O

and,' , "

Target

to

"SUbsequent

,

more

than

~ne

Bus

,

NON-ARBITRATING

,

The

transfer

is

from ,

Target

asserts,

,Ini

tiator.

"users.

,

"

Set

Delay

after

Bus

SYSTEMS:

In systems "

ini

tiator

to

Target

,

MSG

during

the

REG/ACK

handshake

of

"

C/O

and

I/O

" ,

Free

Phase

has

'

·th

th

b't

t'

" ,

this

phase.

, d

deas

rts

T t ,

r'

-Inl'tl'ator

release

l

, been

detected.

The

,

~~ase

n~tAr

1

ra

10n " r

=~G duri~;

, r-

arget

asser

s r

,

I t

,

I--

HANDSHAKE

~

HANDSHAKE

PROCED"RE.·

" , "

C/O.

I/O, and , ,

aWl}.

tlhb"

UnSaSBigunsalS

,

nitia

or

asserts

BSY

implemented

after

I

,L,

the

handshake,

,MSG

during ,

,

and

its

own

SCSI

,

detecting

the

Bus

Free

"

PROCEDURE:

, "

Of

this

Phase"

,the

REQ/ACK

':

Clear

Delay ,

,

device

10

bit

on

the'

Phase

the

Initiator

,I--

The

Target

asserts

~

The

Target

first

drives

data

17-0.P) , , " handshake

(s)

, ,

after

BSY

,

,

data

bus

'waits

a

minimum

of

"

REG.

The

Initiator

I

to

their

desired

values

walts

at

, ,

of

this

phase.

t becomes ,

L--

The

Initiator

waits

, one

Bus

Clear

Delay. "

drives

data

(7-0.P)

to

,

least

one deskew

delay

plus

a

cable

" Only one

byte',

,

'continuously

,

,

an

Arbitration

Delay'

Then

it

asserts

the

data"

tMt

d~s:redt

values.

, skew

delay

then

asserts

REG

Data

,'of

status

is

, r

The

message

,I

false

for

a

BUS

,

, then

examines

the

, bus with

both

the

,,;a,/

ad

leas

lone I

17-0.P)shall

remain

valid

until

ACK

,'transferred.

,

,byte

could

"settle

Delay ,

,

data

bus.

If

a

higher

I

desired

initiator

IO

bit"

es

ew

e

a~

~

us a I

is

true

at

the

Target.

, ,

',indicate,

' ,

priority

SCSI

device'

and

the

Tar:get's

10

bit."

~~~;~t~k!~K.;h:Y

and L

I"

,COMMAND

1

r'

_

The

following

"

10

bit

is

true

on

the,

After

two

deskew

'!

'Inlt

iator

continues

to

r See

handshake,

,COMPLeTE (00). ,

data

bus

(OB7

is

the,

delays

the

Initiator

(',

drive

data

(7-0.P)

until

,he

Initiator

shall

reM

data

(7-0.p)

,procedure

" , ' phase

will

be ,

highest)

the

initiator,

,

asserts

SEL.

~

)

'I

after

REQ

is

true

then

asserts

ACK',

under Data

in

,

~nhaAsreblitfration

,

loses

arbitration

and , " ,

REG

is

false.

phase , , , r

releases

BSY.

11

no :

I'

ARBITRATION

SYSTEMS:

) , L

When

ACK

becomes

true

at

the

Target

, ,L See handshake : '

~m~!~~e~~ed.

or

:

higher

priority

SCSI

, , In systems

with

Arbitration'

L

Wh

n

ACK

s

true

at

I,

the

Target

may

change

or

!'elease

data'

procedure

"p~ase

I ,

device

ID

bit

is

true

,Phase

implemented , , e , (7-0.P) and

deassert

REG'

under Data

in

on

the

data

bus ,

the

in

i

tiator

that

won

"the

Target

the

Target

,

then

the

ini

tiator

"arbitration

has

both

"reads

the

data

(7-0,

P),

:

phase.

wins

arbitration

and , ,

BSY

and

SEL

asserted

'I

then

deasserts

REG.

f--

A

fter

REG

is

false

the

Ini

tiator

,

asserts

SEL.

, :

~~~

~~~~~e~w~h:u~ata

, I ,

deasserts

ACK.

After

ACK

is

false

the

r--

Bus

devices

having

',settle

Delays.

The

' L

When

REG

becomes I

Target

may

continue

the

transfer

by

,

lost

arbitration

Shall',

,

data

bus

is

then "

false

at

the

Initiator

,

driving

data

(7-G,P) and

asserting

,

release

BSY

and

"asserted

with both

the

"the

Initiator

may

,

REG.

,

their

own

SCSI

,

initiator

ID

bit

and

the

" change

or

pelease

data

,

,

deviceIDbitwithin',

desired

Target's

IObiL

,I

(7-0.P)

anddeassertACK.

,

,

a

Bus

Settle

Delay

',T

.. O deskew

delays

, ,

f--

OA,A

au'

PHASE:

Write

Peripheral.

,

after

Sel

becomes

',later

BSY

is

released,

, , ,

~

~~e

~nitiator

that

!

~

IN

ALL

SYSTEMS:

THE

:

~

The

Target

continues

:-

~~~~ei~

to

be

sent

from

Initiator

to

, wins

arbitration

,'Target

determines

that

'

requesting

command

,

wal'ts

at

least

a

Bus

, '

",

bytes.

The

number of L

,arget

deasserts

C/O.

I/O. and

MSG

it

is

selected

when

,bytes

depends

on

the

,

during

the

REG/ACK

handshake of

this

,

Clear

Delay

plus

,'SEL

and

its

SCSI

"

command

group code , phase. Refer

to

the

handsha~e

, a

Bus

Settle

Delay

,'device

ID

bit

are

true

,'detected

from

the

first

! procedure of

the

Command

Phase.

,

after

asserting

Se

I , ' and

BSY

and I/O

are

,'command

byte

recieved.

before

changing

any

, i

false

for

at

least

a

Bus

,!

signals

on

the

b"s,

,Settle

Delay.

The

,

,

Target then

asserts

,

,

BSY

within

a

Selection

'

i Abort Time. :

I--

Two

deskew

delays

,

,

after

the

initiator

,

,

detects

BSY

true

it

I

I

re

leases

SEL

and

may

,

!

change

data

bus

signals.

!

Note:

DB

(P)

- Data

pa!'lty

(odd)

Parity

is

not

valid

dur ing

arbitration.

SCSI Interface

4-7

FIGURE

4-2

SCSI

Bus

Timing

Diagram

Loading...

Loading...