BIOS Setup Utility

SY-7VBA133U

61

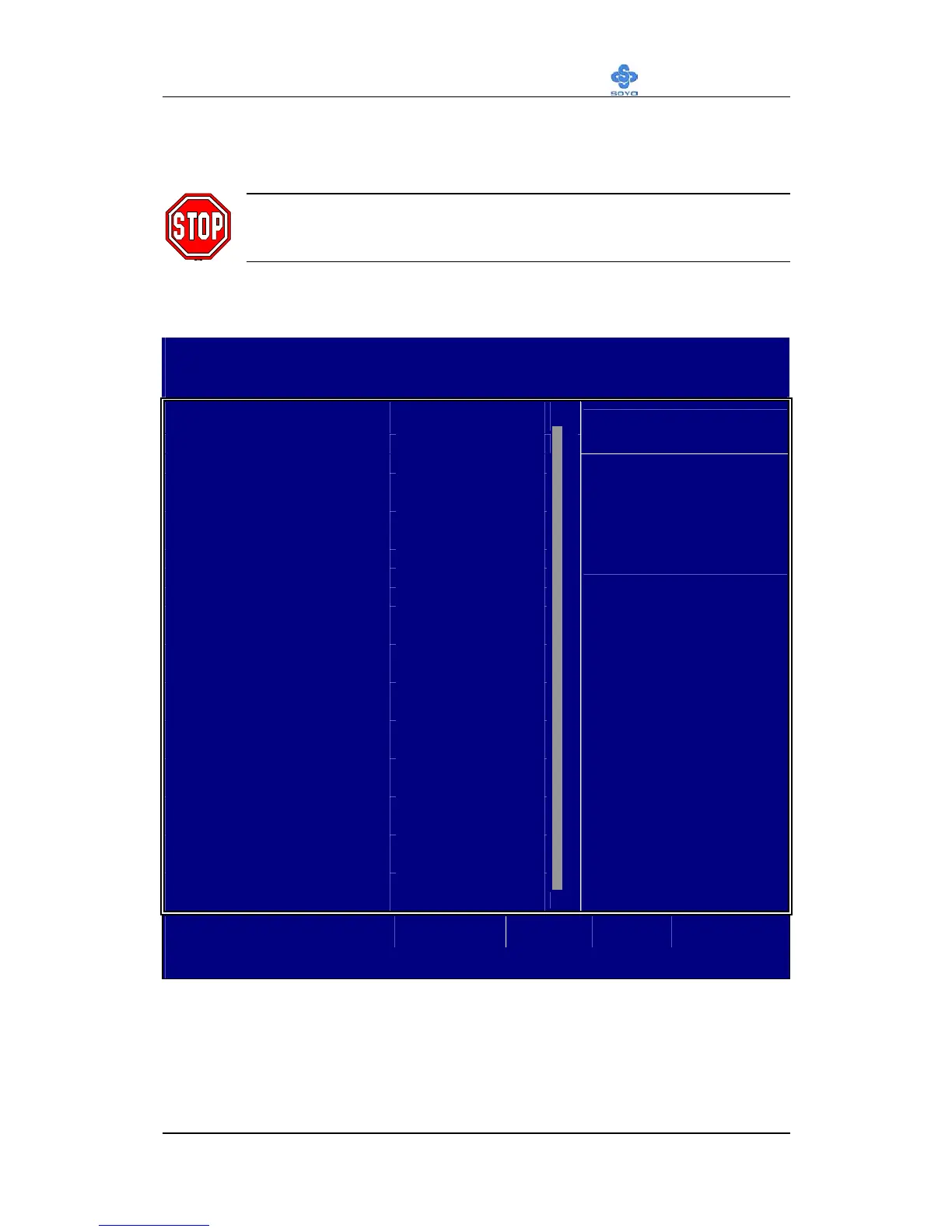

3-4 ADVANCED CHIPSET FEATURES

Caution:

Change these settings only if you are already familiar

with the Chipset.

The [Advanced Chipset Features] option changes the values of the chipset

registers. These registers control the system options in the computer.

CMOS Setup Utility – Copyright ( C ) 1984-2001 Award Software

Advanced Chipset Features

DRAM Timing By SPD Enabled

x DRAM Clock Host CLK

Item Help

x SDRAM Cycle Length 3

x Bank Interleave Disabled

Memory Hole Disabled

P2C/C2P Concurrency Enabled

Fast R-W Turn Around Enabled

CPU IOQ Size 4 Level

System BIOS Cacheable Disabled

Video BIOS Cacheable Disabled

Video RAM Cacheable Disabled

AGP Aperture Size 128M

AGP-4X Mode Enabled

AGP Driving Control Auto

x AGP Driving Value DA

AGP Fast Write Disabled

OnChip USB Enabled

USB Keyboard Support Disabled

CPU to PCI Write Buffer Enabled

PCI Dynmic Bursting Enabled

PCI Master 0 WS Write Enabled

PCI Delay Transaction Enabled

PCI#2 Access #1 Retry Enabled

AGP Master 1 WS Write Disabled

AGP Master 1 WS Read Disabled

Memory Parity/ECC Check Disabled

Menu Level

Enabled adds a parity check to

the boot-up memory tests.

Select Enabled only if the

system DRAM contains parity

:Move

Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Fail-Safe Defaults F7: Optimized Defaults

Loading...

Loading...