DocID026304 Rev 3 13/44

AN4488 Power supplies

43

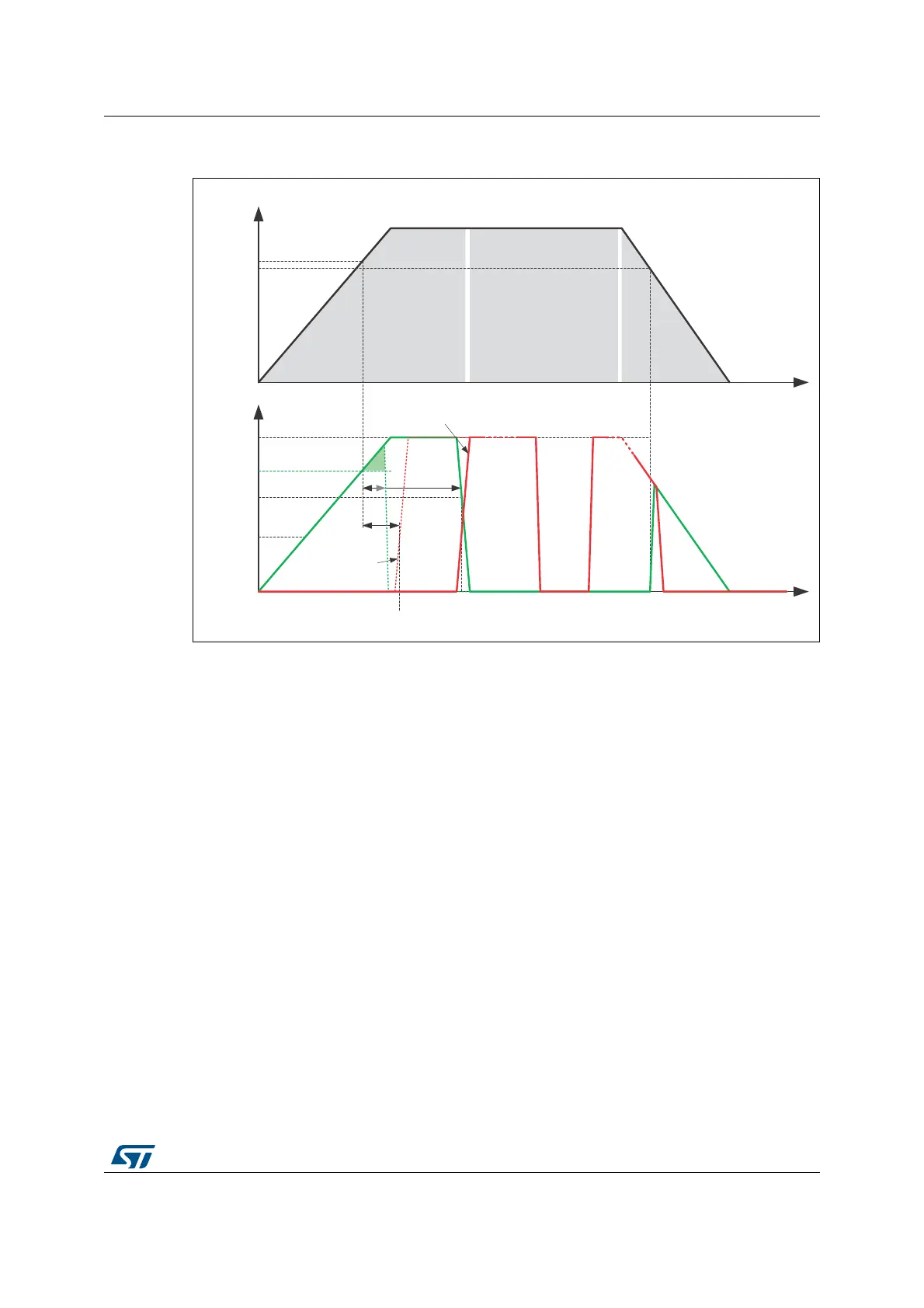

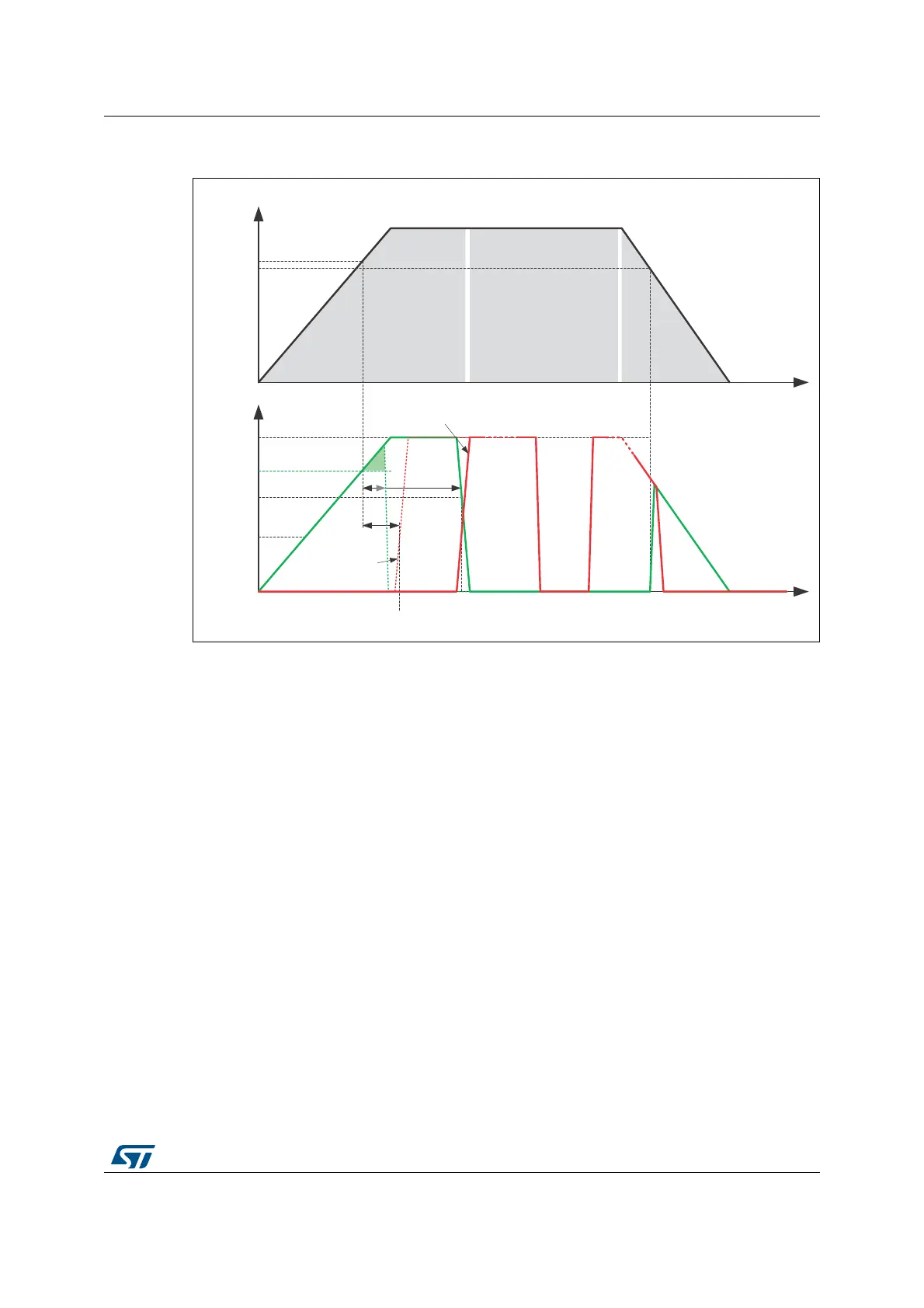

Figure 6. PDR_ON timings example

(not to scale, not needed for STM32F411xx and STM32F446xx)

Selection of PDR_ON voltage supervisor

Voltage supervisor should have the following characteristics

• Reset output active-high push-pull (output driving high when voltage is below trip

point)

• Supervisor trip point including tolerances and hysteresis should fit the expected V

DD

range.

Notice that supervisor spec usually specify trip point for falling supply, so hysteresis

should be added to check the power on phase.

Example:

– Voltage regulator 1.8V +/- 5% mean V

DD

min1.71V

– Supervisor specified at 1.66V +/- 2.5% with an hysteresis of 0.5% mean

- rising trip max = 1.71V (1.66V + 2.5% + 0.5%)

- falling trip min = 1.62V (1.66V - 2.5%).

2SHUDWLRQ 3RZHU'RZQSKDVH3RZHU2QSKDVH

069

9''

WLPH

9

9''GXULQJRSHUDWLRQNHSWDERYH9

3'5B21

WLPH

1567

1567.HSWORZE\

LQWHUQDOFLUFXLWU\

9

9

,/

9

,+

3'5B21PXVW

JRDERYH9

9''

5HVHWE\

LQWHUQDO

VRXUFHV

1567IRUFHGORZE\H[WHUQDO

DQGLQWHUQDOFLUFXLWU\

VXSHUYLVRU

ORZWULSSRLQW

VXSHUYLVRU

KLJKWULSSRLQW

1567.HSWORZE\

H[WHUQDOVXSHUYLVRU

7

VXSHUYLVRU

7

5677(032

7

VXSHUYLVRU!

7

5677(032

7

5677(032

7

VXSHUYLVRU

Loading...

Loading...