Reference design AN4488

40/44 DocID026304 Rev 3

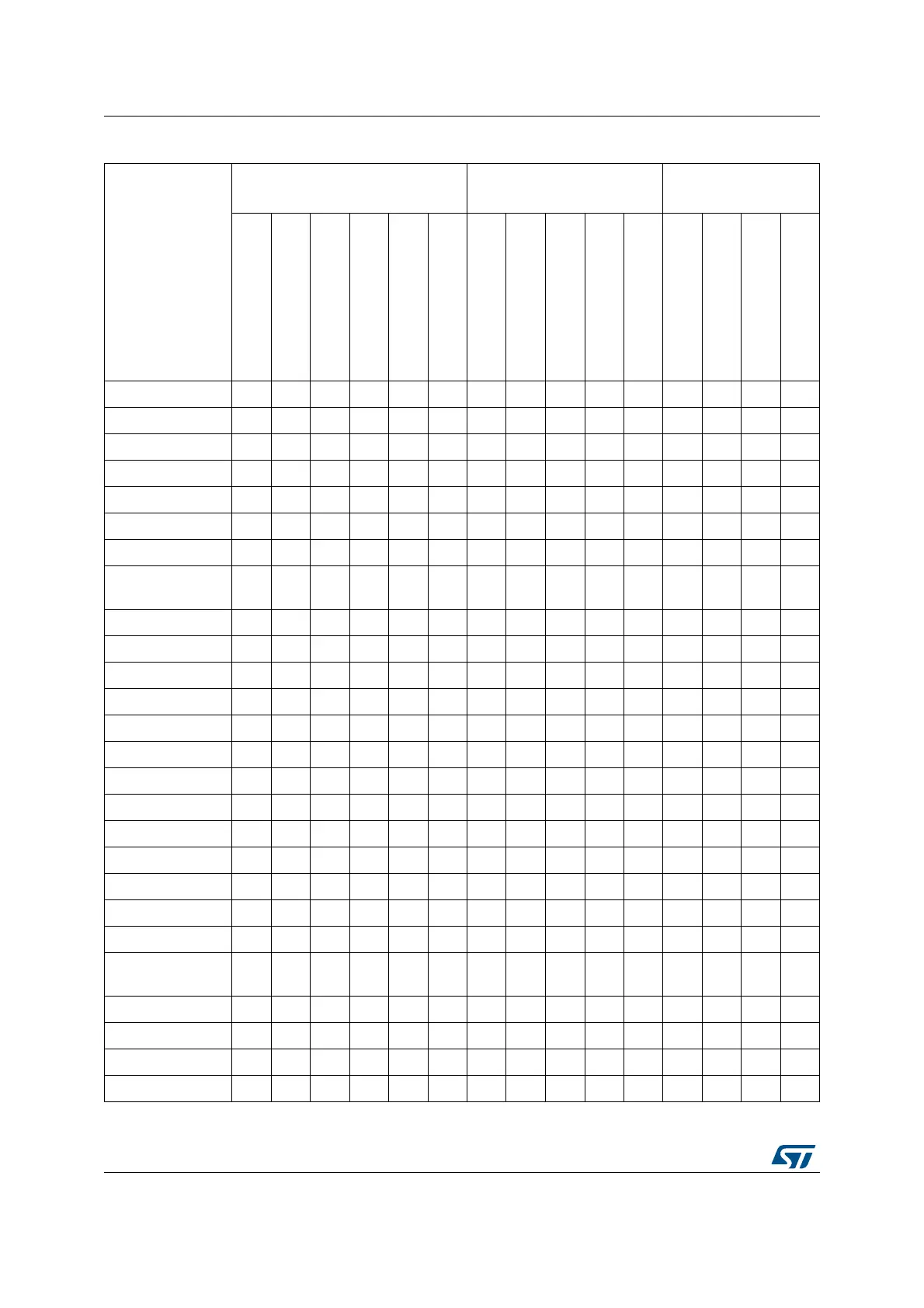

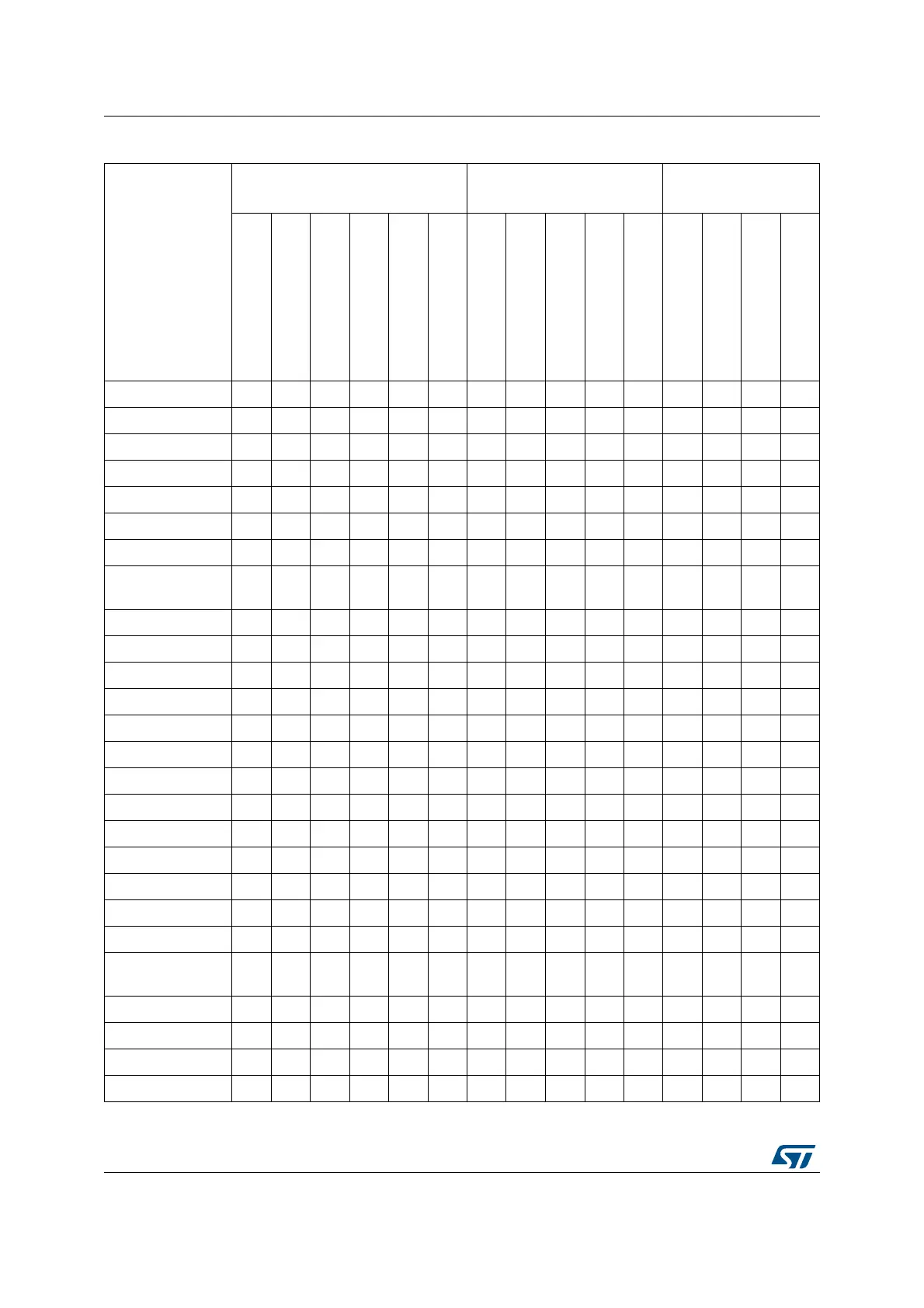

Table 12. Reference connection for all packages

Pin Name

Pin Numbers for packages with

pins on 4 edges

Pin Numbers for BGA

Packages

Chip Scale Packages

48 pins

64 pins

(1)

100 pins

(1)

144 pins

(2)

176 pins

208 pins

100 pins

144 pins

169 pins

176 pins

216 pins

49 pins

81 pins

90 pins

143 pins

PA13 34 46 72 105 124 147 A11 A12 E12 A15 A15 B3 D2 D4 D3

PA14 37 49 76 109 137 159 A10 A11 A11 A14 A14 A1 C3 A2 B1

PA15 38 50 77 110 138 160 A9 A10 B11 A13 A13 A2 B2 B3 C2

PB2 20 28 37 48 58 63 L6 J5 L5 M6 M5 G3 J6 J7 L7

PB3 39 55 89 133 161 192 A8 A7 B6 A10 A10 A3 A5 B6 B7

PB4 40 56 90 134 162 193 A7 A6 A6 A9 A9 A4 B5 A6 C7

PC14-OSC32_IN 3 3 8 8 9 9 D1 B1 E1 E1 E1 C7 C9 B10 D11

PC15-

OSC32_OUT

4 4 9 9 1010E1C1F1F1F1C6D9B9E11

PH0 - OSC_IN 5 5 12 23 29 32 F1 D1 G2 G1 G1 D7 E9 F10 J11

PH1 - OSC_OUT 6 6 13 24 30 33G1E1G1H1H1D6F9F9H10

BOOT0 44 60 94 138 166 197 A4 D5 A5 D6 E6 A5 A7 A7 C9

NRST 7 7 14 25 31 34 H2 F1 H2 J1 J1 E7 D8 G10 H9

BYPASS_REG - - - - 48 - E3 H5 M1 L4 L5 - J8 D9 N11

PDR_ON - - - 143 171 203 H3 E5 C3 C6 E5 B6 B8 A8 A11

VBAT 1 1 6 6 6 6 E2 C2 E5 C1 C1 B7 B9 A10 C11

VDDA - - 22 33 39 42 M1 M1 J4 R1 R1 - - - L10

VREF+ - - 21 32 38 41 L1 L1 J3 P1 P1 - - - L11

VDDA/VREF+913---------F7H8G9-

VSSA ------J1J1J1M1N1----

VREF- ------K1K1J2N1N1----

VSSA/VREF- 8 12 20 31 37 40 - - - - - E6 F7 H10 K10

VDDUSB33 - - -

-

(95)

---C11----E1--

VDD - - - - 15 15 - - F4 F3 F4 - - - E10

VDD - - 11 17 23 26G2D3G8G3H5 - - B8 -

VDD - - 19303639 - - - - J5 - H9 - G7

VDD - 19 28 39 49 52 - F4 J11 K4 K5 - - E4 J8

Loading...

Loading...