3-59

The output from U770A is applied directly to sampling

switch U560A, an enhancement-mode MOS-FET device.

The switch gate is controlled via 0660 by the OSAM1

(Output Sample from Channel 1) logic signal, and is closed

when the data being Shifted out of the CCD is stable.

When OSAM1 is LO, the switch is on, and hold capacitor

C561 charges to the signal level of U770A. When OSAM1

is HI, the switch is off, and C561 holds its voltage level.

Figure 3-3 (shown previously in the "System Clocks"

description) shows the timing of OSAM1 and OSAM2 dur-

ing the Slow-Out and Short-Pipe modes of CCD operation.

During Fast-In mode, OSAM1 and OSAM2 are both

held LO.

Track-and-Hold Amplifiers and Multiplexers

The Track-and-Hold Amplifiers and Multiplexers allow a

single A/D Converter to digitize all the analog samples

from both CCD arrays by time-multiplexing the output

samples to the single converter. The four Track-and-Hold

circuits are identical; and, for brevity, only the CH 1-Side

1 circuitry will be described.

Side 1 signal outputs from U450 are applied through

R876A and R876B to the bases of U775A and U775B.

Transistors U775A and U775B form a differential trans-

conductance amplifier that provides high-impedance load-

ing of the CCD array outputs. The collectors of the two

transistors are connected to operational amplifier U770A

which is configured as a differential-input, single-ended

output transresistance amplifier. The connection of R771

to the

+

7.5 V supply causes the output of U770A to be

level shifted to +7.5 V. The resulting output at pin 1 of

U770A is a level-shifted, attenuated, single-ended replica

of the differential CCD array output signal with most

common-mode interference removed.

Single-Ending Amplifiers

There are four identical Single-Ending Amplifiers used

to convert the four differential CCD array outputs to

single-ended signals for A/D conversion. Operation of the

Channel 1-Side 1 Single-Ending Amplifier is described.

The CCD Output circuits (diagram 14) convert the two

differential output signals from each CCD into single-ended

signals for subsequent AID conversion. The single-ended

analog voltages are applied to Track-and-Hold circuits

where they are held until the time-multiplexed A/D Con-

verter digitizes the stored samples.

CCO

OUTPUT

Theory of Operation-2430 Service

As the CALCLK signal goes from LO to HI, the base of

U831D is pulled HI, reverse biasing U831C. Bias current

for 0831 now flows through R834 and R835, turning it on.

The voltage at the emitter of 0831 rises to a level of +2.4

volts, determined by the voltage regulator composed of

U731, U831A, U831B, 0831, and associated components.

This regulated level is divided down to +400 mV p-p, by

the resistive divider formed by R832 and R831, and

applied to the front-panel CALIBRATOR loop at an

Gffectiveoutput impedance of 50 ohms.

When the CALCLK (calibrator clock) signal, at the base

of U831D (applied via R885) is LO, U831C (configured as

a diode) is forward biased. This shunts bias current away

from 0831, keeping it turned off. When 0831 is off, the

front-panel CALIBRATOR output is pulled to ground

potential, through R831, thereby setting the lower limit of

the CALIBRATOR square-wave signal.

The Calibrator circuit is composed of U731, U831,

0831, and associated components. Output frequency is

set by the CALCLK signal from the Time Base Controller

(diagram 8). The output frequency follows the SEC/DIV

setting from 50 ns/div to 20 rns/div and is set to display

from 2.5 to 10 calibrator cycles across the ten graticule

divisions over those settings. This feature allows quick and

easy verification of the acquisition time base rates. The

Calibrator circuitry is essentially a voltage regulator that is

switched off and on, producing a square-wave output sig-

nal at the CALIBRATOR loop.

Calibrator

620F Read Jitter Correction Counter 2

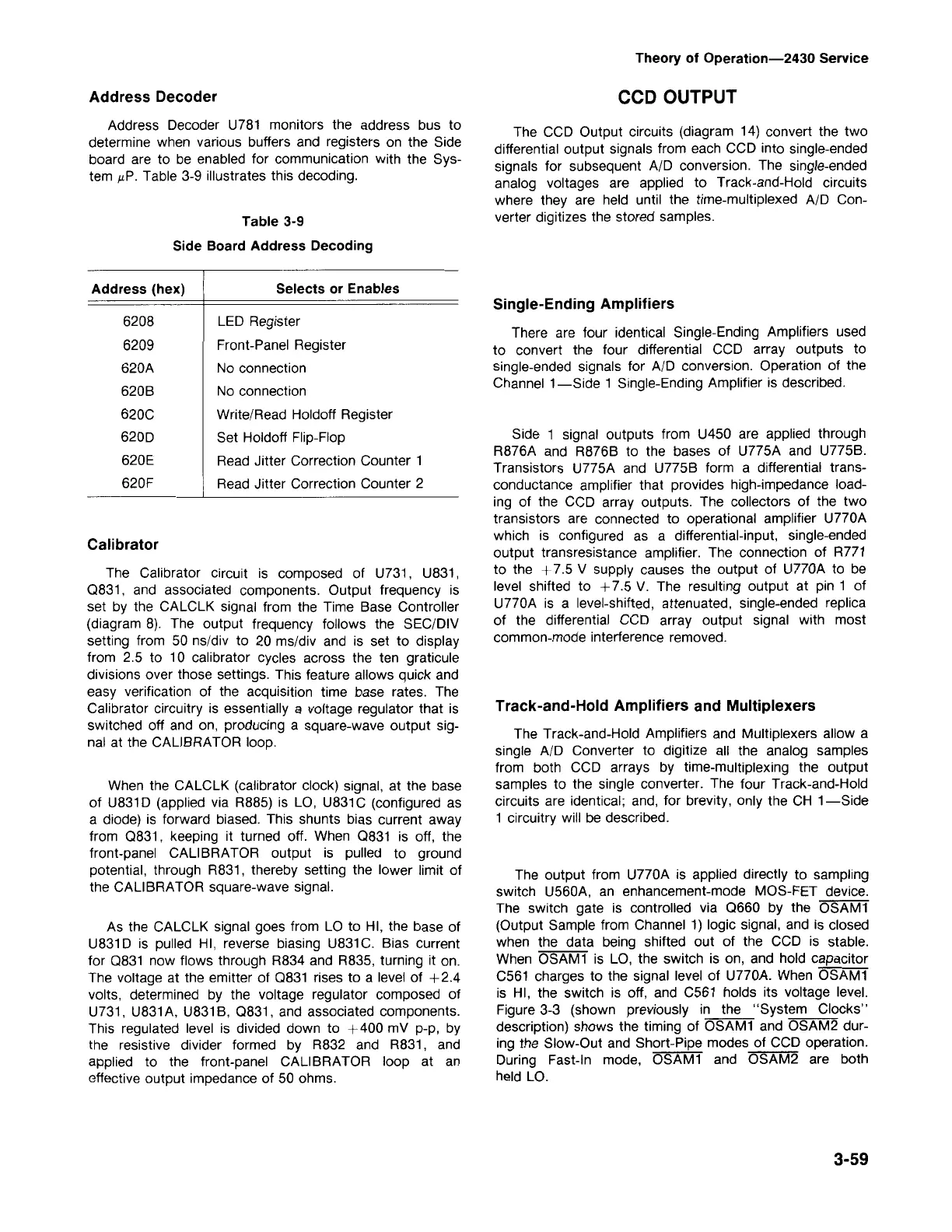

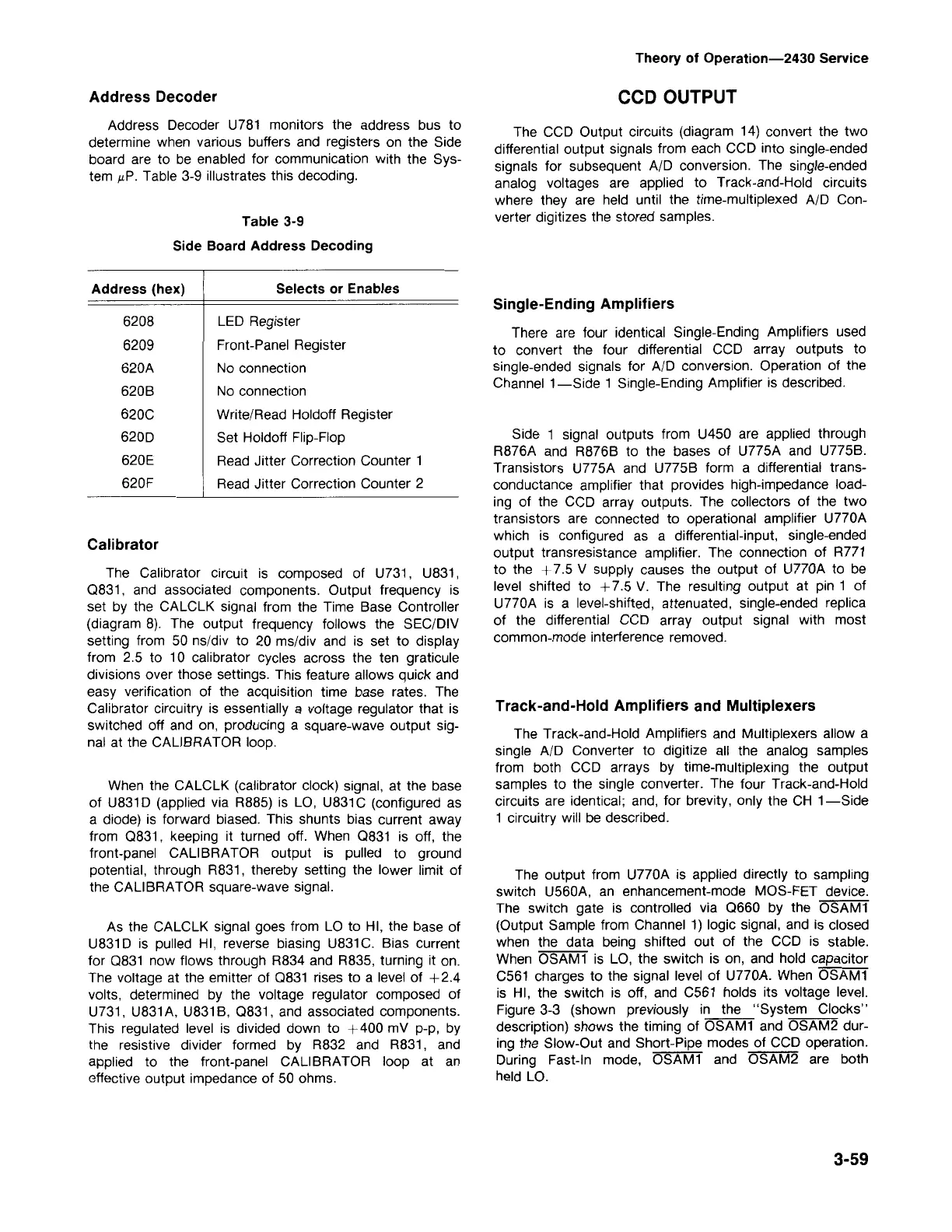

6208

6209

620A

620B

620C

620D

620E

Selects or Enables

LED Register

Front-Panel Register

No connection

No connection

Write/Read Holdoff Register

Set Holdoff Flip-Flop

Read Jitter Correction Counter 1

Address (hex)

Table 3-9

Side Board Address Decoding

Address Decoder U781 monitors the address bus to

determine when various buffers and registers on the Side

board are to be enabled for communication with the Sys-

tem /-LP.Table 3-9 illustrates this decoding.

Address Decoder

Loading...

Loading...