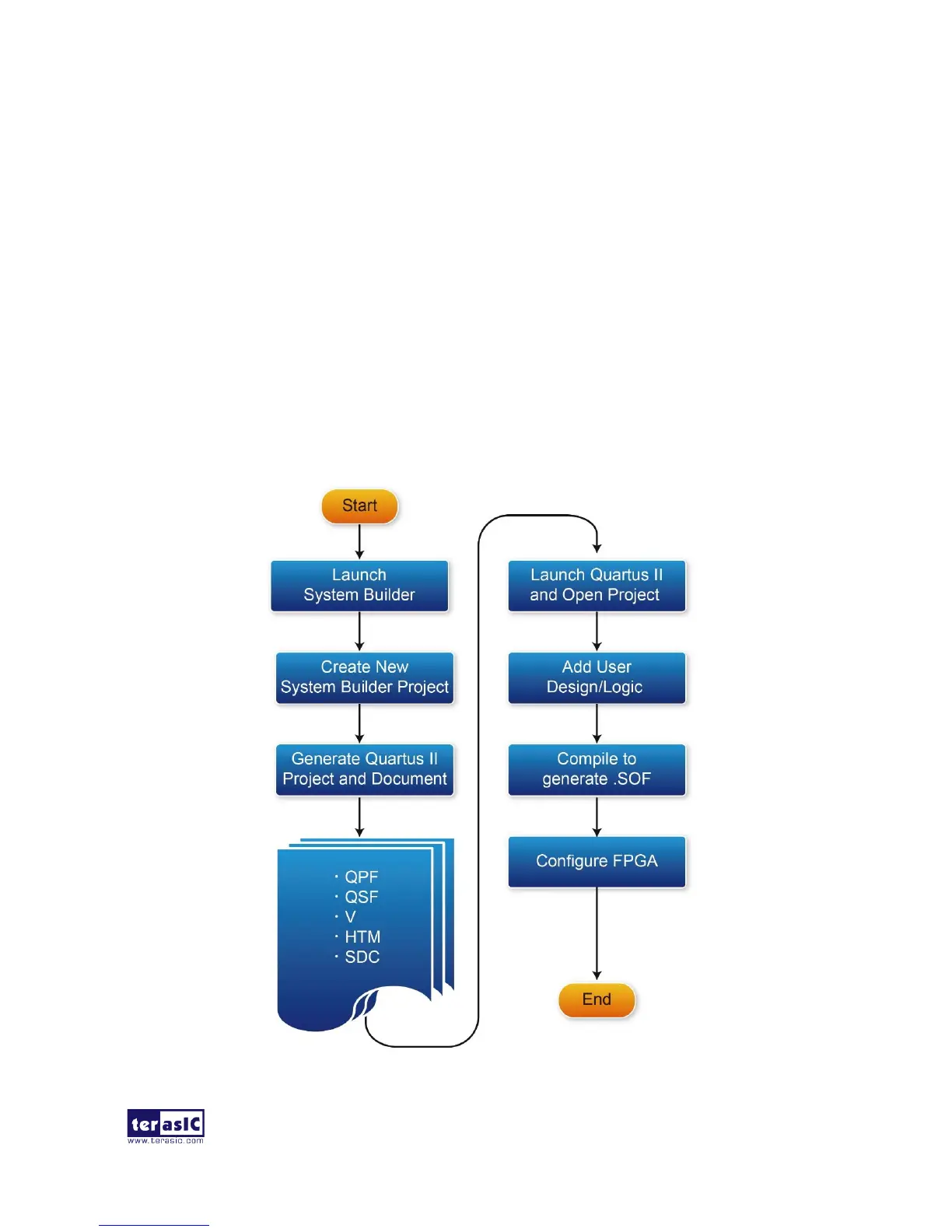

This section provides an introduction to the design flow of building a Quartus II project for

DE10-Lite under the DE10-Lite System Builder. The design flow is illustrated in Figure 4-1.

The DE10-Lite System Builder will generate two major files, a top-level design file (.v) and a

Quartus II setting file (.qsf) after users launch the DE10-Lite System Builder and create a new

project according to their design requirements.

The top-level design file contains a top-level Verilog HDL wrapper for users to add their own

design/logic. The Quartus II setting file contains information such as FPGA device type, top-level

pin assignment, and the I/O standard for each user-defined I/O pin.

Finally, the Quartus II programmer is used to download .sof file to the development board via JTAG

interface.

Figure 4-1 Design flow of building a project from the beginning to the end

Loading...

Loading...