Testing the EVM in Digital Time Gain Compensation (DTGC) Mode

www.ti.com

16

SLOU489–August 2017

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

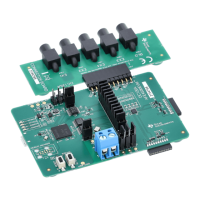

AFE5832 32-Channel Analog Front-End Evaluation Module (EVM Rev. A)

Figure 17. DTGC Mode Test: Trigger Options

g. Change the ADC Output Data Rate to '20M' and the ADC Input Target Frequency to '5M'. Set the view

display to ‘Codes’.

Figure 18. DTGC Mode Test: HSDC Pro Test Parameter Settings

h. Press the Capture button on HSDC Pro.

i. The Up-Down Ramp DTGC waveform should appear similar to Figure 19.

Figure 19. DTGC Mode Test: Waveform