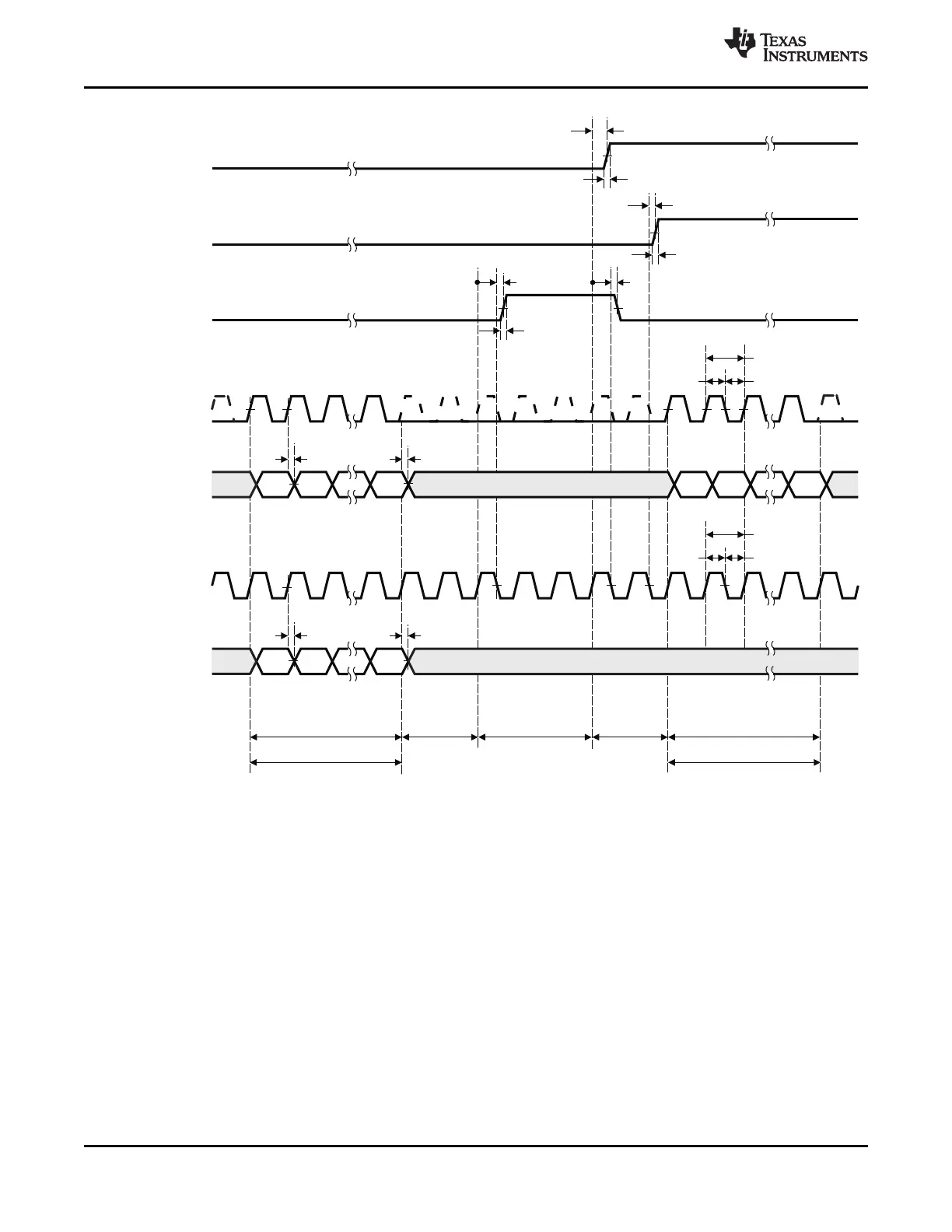

LCD_HSYNC

LCD_PCLK

(active mode)

LCD_D [23:0]

(active mode)

ATA

1, L

P, L

2, L

PPLMSB + PPLLSB

16 x (1 to 2048)

HBP

(1 to 256)

Line L

(1 to 256)

HFP

(1 to 64)

HSW

Line 1 (Passive Only)

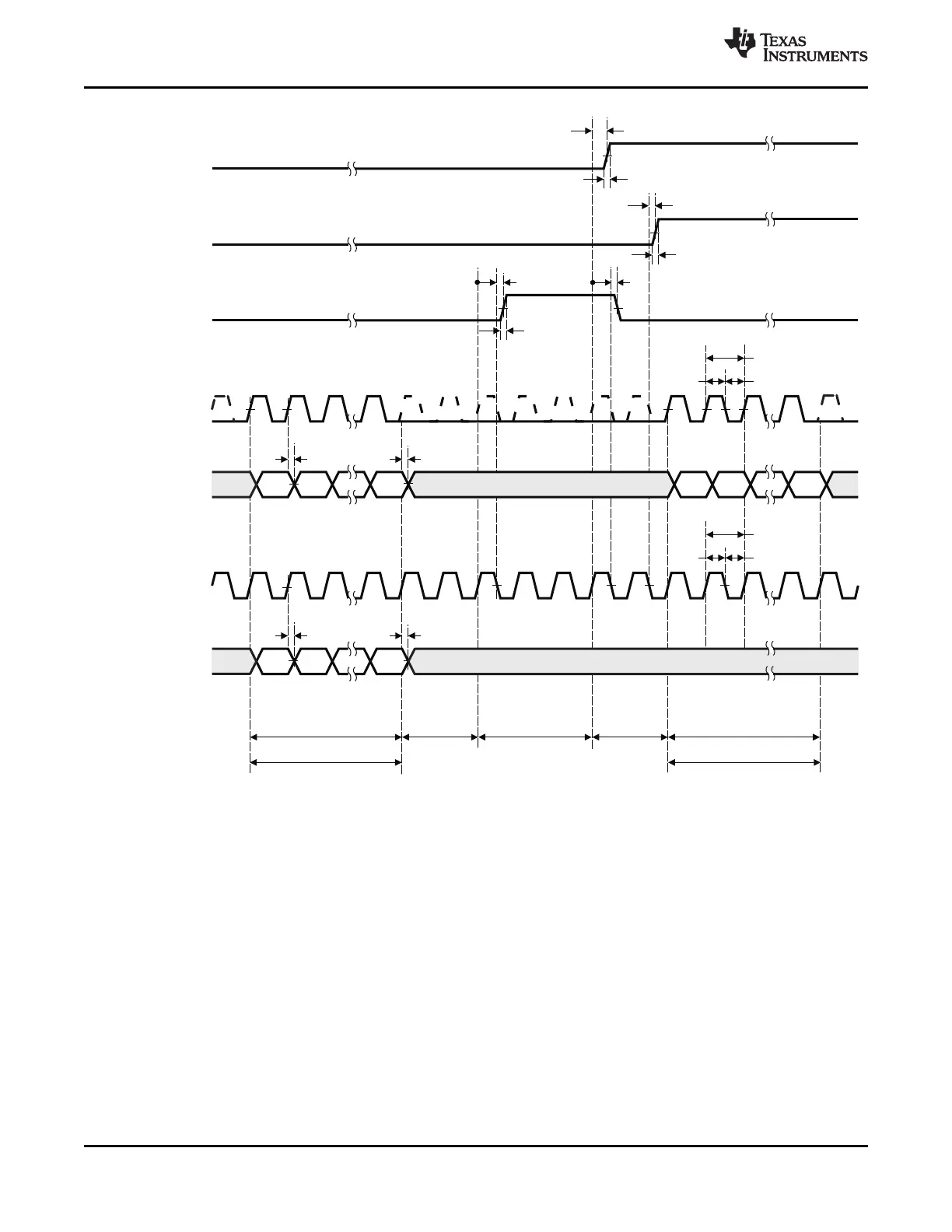

LCD_VSYNC

LCD_PCLK

(passive mode)

LCD_AC_BIAS_EN

LCD_D [7:0]

(passive mode)

ATA

1, L 2, 1

P, 1

P, L

2, L

1, 1

10

10

8

6

4

5

1

2 3

VBP = 0

VFP = 0

VWS = 1

1

2 3

4

5

PPLMSB + PPLLSB

16 x (1 to 2048)

7

9

11

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

SPRS717H –OCTOBER 2011–REVISED MAY 2015

www.ti.com

A. The dashed portion of LCD_PCLK is only shown as a reference of the internal clock that sequences the other signals.

Figure 7-84. LCD Raster-Mode Control Signal Activation

208 Peripheral Information and Timings Copyright © 2011–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...