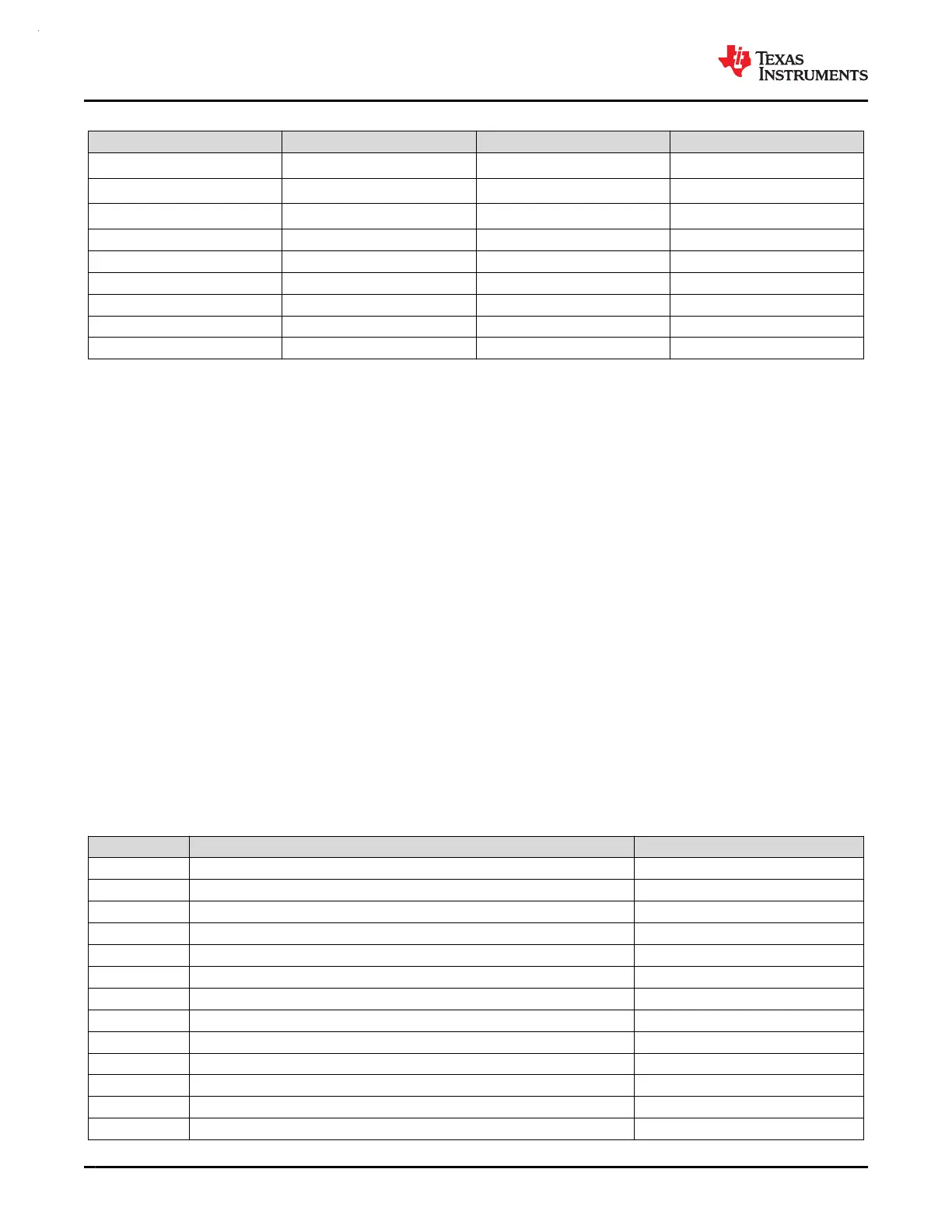

Table 8-2. DMA Trigger Mapping (continued)

Trigger 0:12 Source Trigger 13:24 Source

4 AES Publisher 2 17 UART0 Publisher 1

5 AES Publisher 3 18 UART0 Publisher 2

6 DAC0 Publisher 2 19 UART1 Publisher 1

7 I2C0 Publisher 1 20 UART1 Publisher 2

8 I2C0 Publisher 2 21 UART2 Publisher 1

9 I2C1 Publisher 1 22 UART2 Publisher 2

10 I2C1 Publisher 2 23 ADC0 Publisher 2

11 SPI0 Publisher 1 24 ADC1 Publisher 2

12 SPI0 Publisher 2

For more details, see the DMA chapter of the MSPM0 G-Series 80-MHz Microcontrollers Technical Reference

Manual.

8.6 Events

The event manager transfers digital events from one entity (for example, a peripheral) to another (for example, a

second peripheral, the DMA, or the CPU). The event manager implements event transfer through a defined set

of event publishers (generators) and subscribers (receivers) which are interconnected through an event fabric

containing a combination of static and programmable routes.

Events which are transferred by the event manager include:

• Peripheral event transferred to the CPU as an interrupt request (IRQ) (Static Event)

– Example: RTC interrupt is sent to the CPU

• Peripheral event transferred to the DMA as a DMA trigger (DMA Event)

– Example: UART data receive trigger to DMA to request a DMA transfer

• Peripheral event transferred to another peripheral to directly trigger an action in hardware (Generic Event)

– Example: TIMx timer peripheral publishes a periodic event to the ADC subscriber port, and the ADC uses

the event to trigger start-of-sampling

Refer to Event chapter of the MSPM0 G-Series 80-MHz Microcontrollers Technical Reference Manual for more

information.

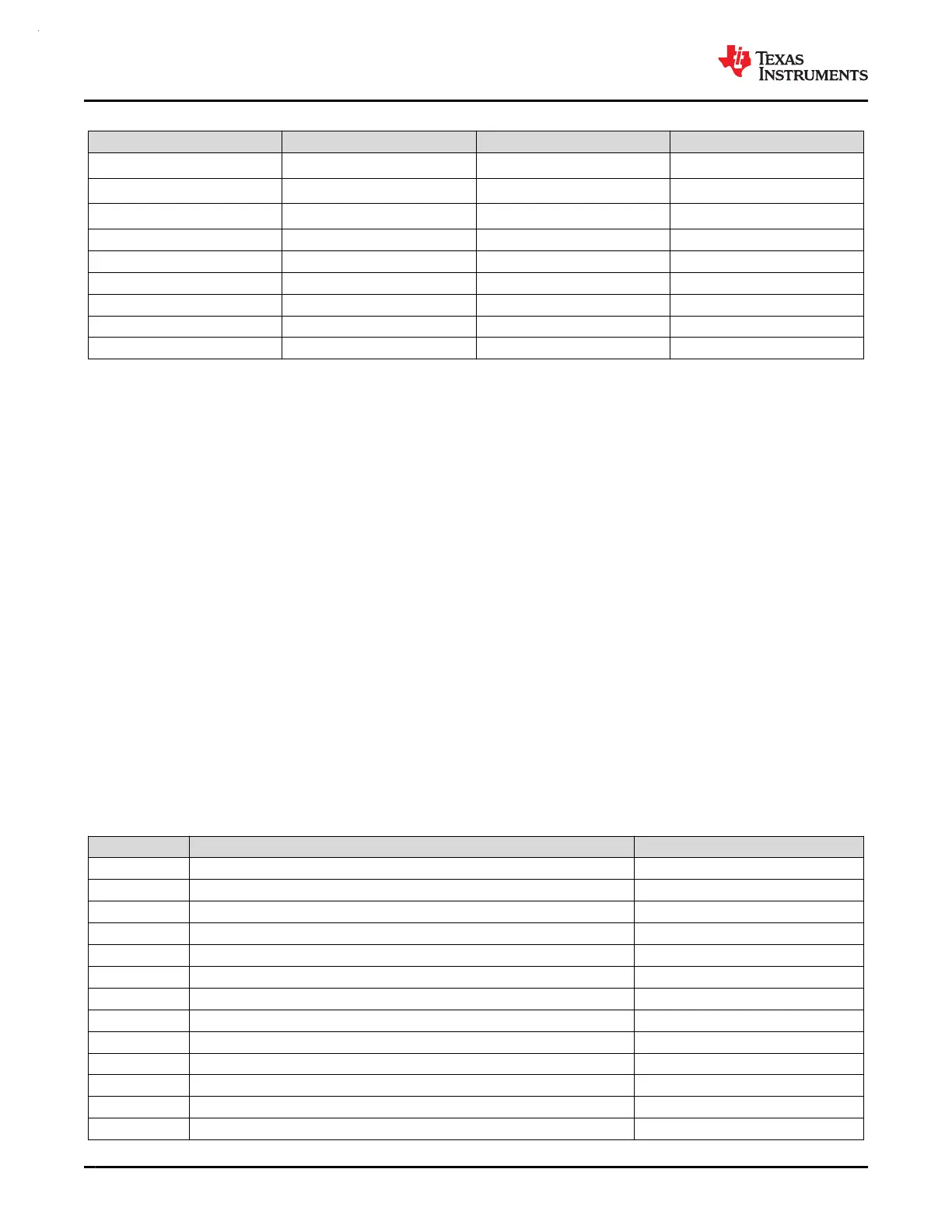

Table 8-3. Generic Event Channels

A generic route is either a point-to-point (1:1) route or a point-to-two (1:2) splitter route route in which the peripheral

publishing the event is configured to use one of several available generic route channels to publish its event to another entity

(or entities, in the case of a splitter route), where an entity may be another peripheral, a generic DMA trigger event, or a

generic CPU event.

CHANID Generic Route Channel Selection Channel Type

0 No generic event channel selected N/A

1 Generic event channel 1 selected 1 : 1

2 Generic event channel 2 selected 1 : 1

3 Generic event channel 3 selected 1 : 1

4 Generic event channel 4 selected 1 : 1

5 Generic event channel 5 selected 1 : 1

6 Generic event channel 6 selected 1 : 1

7 Generic event channel 7 selected 1 : 1

8 Generic event channel 8 selected 1 : 1

9 Generic event channel 9 selected 1 : 1

10 Generic event channel 10 selected 1 : 1

11 Generic event channel 11 selected 1 : 1

12 Generic event channel 12 selected 1 : 2 (splitter)

MSPM0G3507, MSPM0G3506, MSPM0G3505

SLASEX6A – FEBRUARY 2023 – REVISED JUNE 2023

www.ti.com

56 Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: MSPM0G3507 MSPM0G3506 MSPM0G3505

Loading...

Loading...