112

TMS320F28069

,

TMS320F28068

,

TMS320F28067

,

TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698F –NOVEMBER 2010–REVISED MARCH 2016

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

Detailed Description Copyright © 2010–2016, Texas Instruments Incorporated

6.9.6.1 McBSP Electrical Data/Timing

6.9.6.1.1 McBSP Transmit and Receive Timing

(1) Polarity bits CLKRP = CLKXP = FSRP = FSXP = 0. If the polarity of any of the signals is inverted, then the timing references of that

signal are also inverted.

(2) 2P = 1/CLKG in ns. CLKG is the output of sample rate generator mux. CLKG = CLKSRG/(1 + CLKGDV). CLKSRG can be LSPCLK,

CLKX, CLKR as source. CLKSRG ≤ (SYSCLKOUT/2). McBSP performance is limited by I/O buffer switching speed.

(3) Internal clock prescalers must be adjusted such that the McBSP clock (CLKG, CLKX, CLKR) speeds are not greater than the I/O buffer

speed limit (20 MHz).

(4) Maximum McBSP module clock frequency decreases to 10 MHz for internal CLKR.

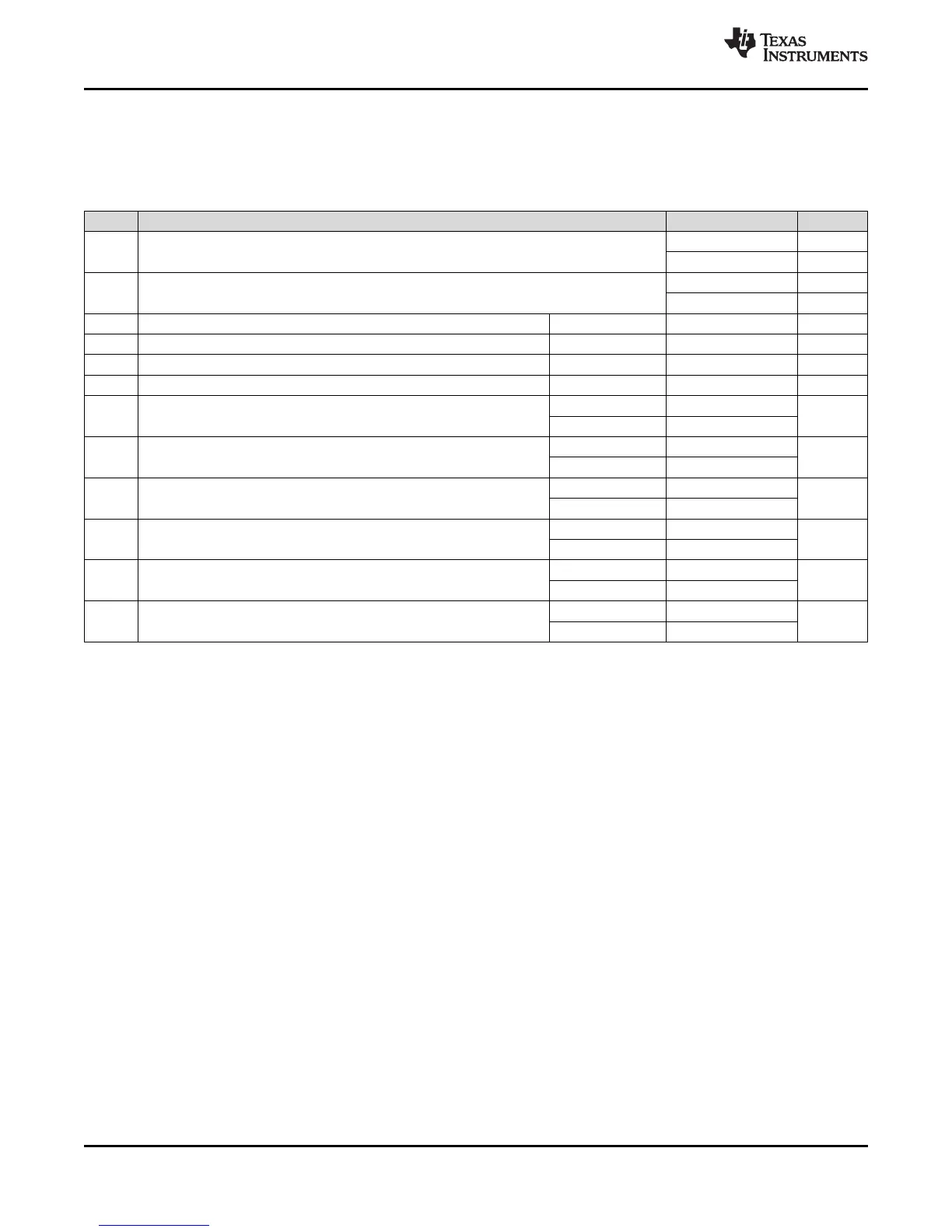

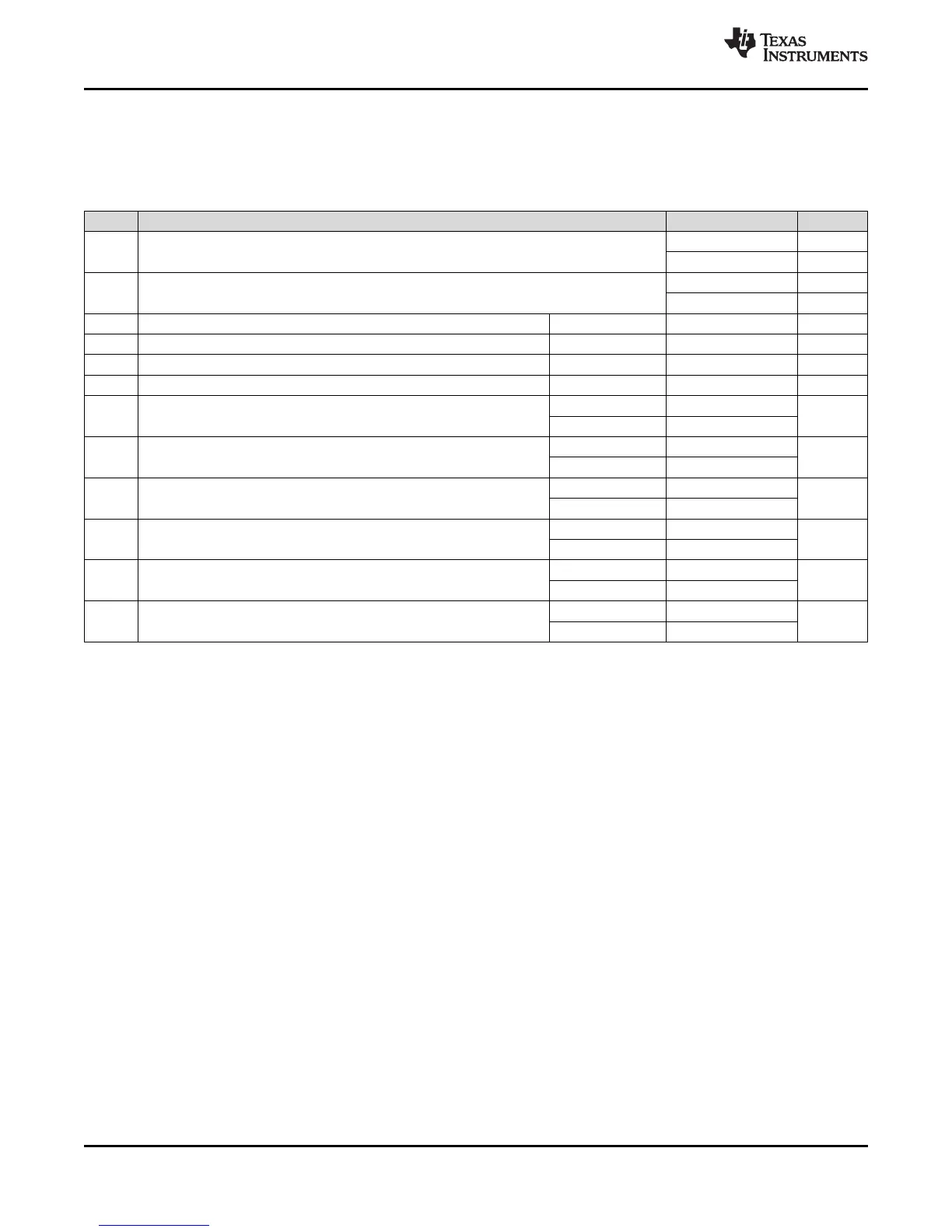

Table 6-42. McBSP Timing Requirements

(1)(2)

NO. MIN MAX UNIT

McBSP module clock (CLKG, CLKX, CLKR) range

1 kHz

20

(3)(4)

MHz

McBSP module cycle time (CLKG, CLKX, CLKR) range

50

(4)

ns

1 ms

M11 t

c(CKRX)

Cycle time, CLKR/X CLKR/X ext 2P ns

M12 t

w(CKRX)

Pulse duration, CLKR/X high or CLKR/X low CLKR/X ext P – 7 ns

M13 t

r(CKRX)

Rise time, CLKR/X CLKR/X ext 7 ns

M14 t

f(CKRX)

Fall time, CLKR/X CLKR/X ext 7 ns

M15 t

su(FRH-CKRL)

Setup time, external FSR high before CLKR low

CLKR int 18

ns

CLKR ext 2

M16 t

h(CKRL-FRH)

Hold time, external FSR high after CLKR low

CLKR int 0

ns

CLKR ext 6

M17 t

su(DRV-CKRL)

Setup time, DR valid before CLKR low

CLKR int 18

ns

CLKR ext 2

M18 t

h(CKRL-DRV)

Hold time, DR valid after CLKR low

CLKR int 0

ns

CLKR ext 6

M19 t

su(FXH-CKXL)

Setup time, external FSX high before CLKX low

CLKX int 18

ns

CLKX ext 2

M20 t

h(CKXL-FXH)

Hold time, external FSX high after CLKX low

CLKX int 0

ns

CLKX ext 6

Loading...

Loading...