72 www.xilinx.com AC701 Evaluation Board

UG952 (v1.3) April 7, 2015

Chapter 1: AC701 Evaluation Board Features

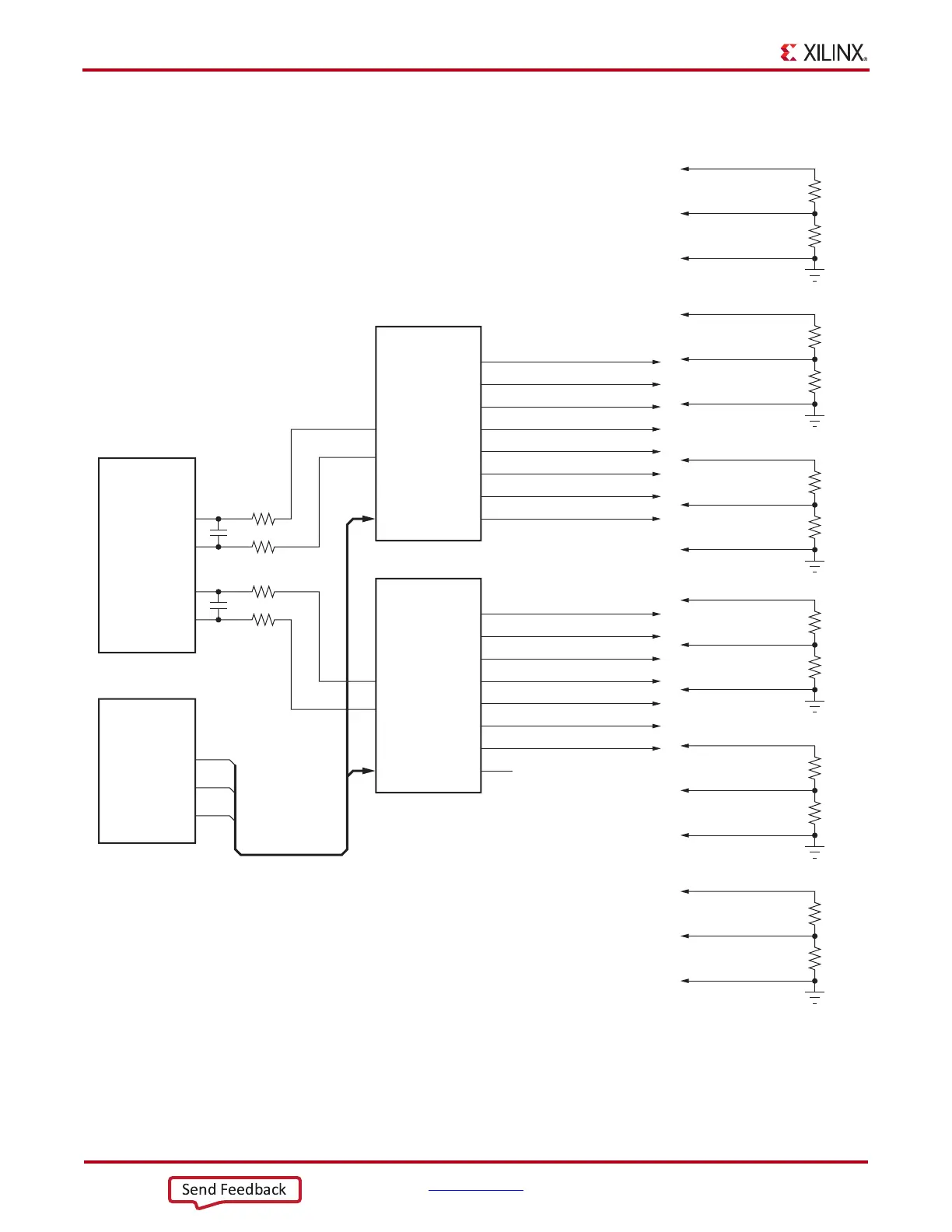

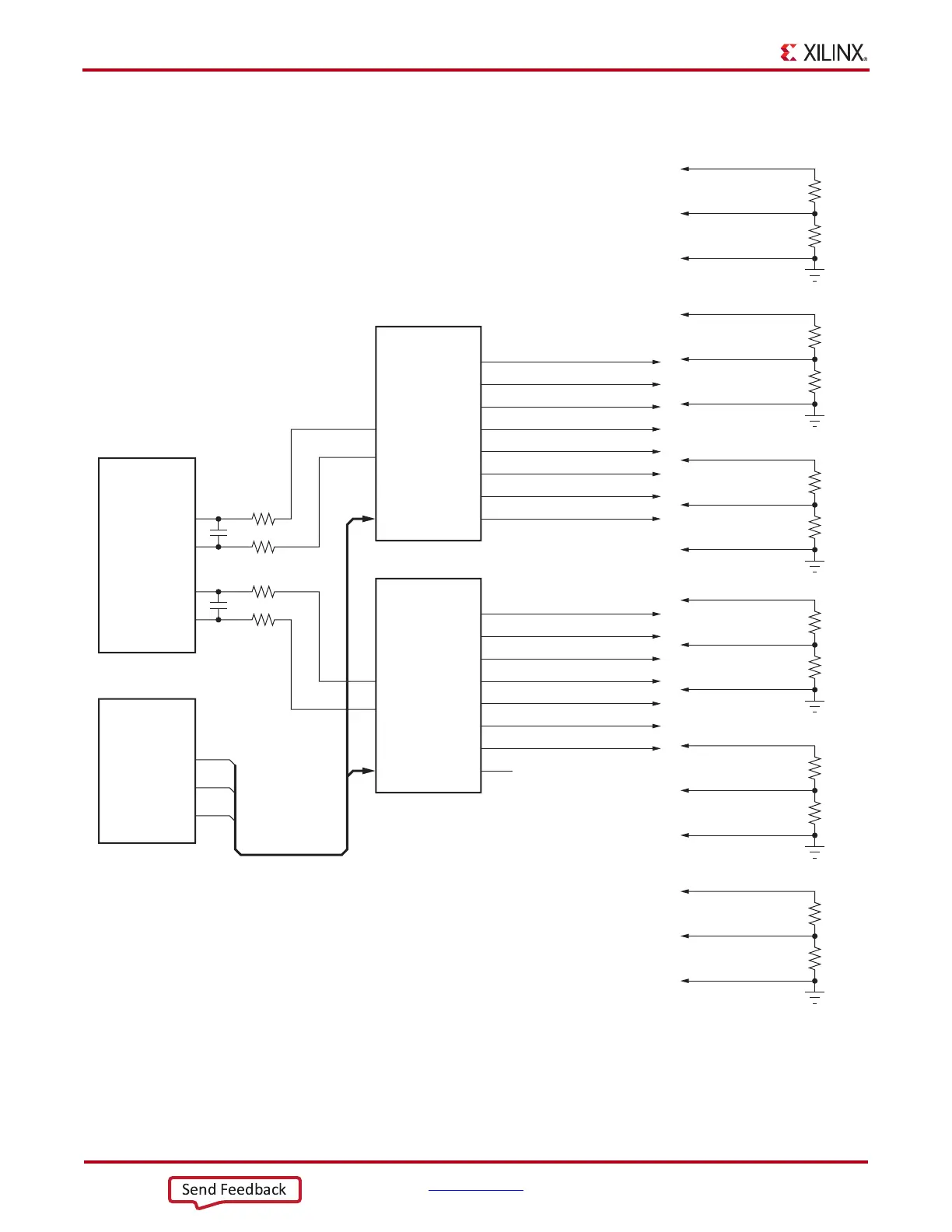

Figure 1-46 shows the XADC external multiplexer block diagram.

X-Ref Target - Figure 1-46

Figure 1-46: XADC External Multiplexer Block Diagram

UG952_c1_139_011813

1. ..._XADC_P/N =Remote voltage sense.

2. ..._XADC_CS_P/N = Current Sense from op amp.

XC7A200T

FPGA

(Bank 15)

U1

ADIP K16

AD1N K17

AD9P M15

AD9N L15

Notes:

49.9

49.9

10 pF

49.9

49.9

10 pF

XC7A200T

FPGA

(Bank 16)

U1

A0 B25

A1 A25

A2 A23

VCCINT_XADC_CS_P/N

VCCAUX_XADC_CS_P/N

VCCBRAM_XADC_CS_P/N

FPGA_1V5_XADC_P/N

FPGA_1V5_XADC_CS_P/N

VCCO_VADJ_XADC_P/N

VCCO_VADJ_XADC_CS_P/N

FPGA_1V8_XADC_P/N

FPGA_1V8_XADC_CS_P/N

FPGA_3V3_XADC_P/N

FPGA_3V3_XADC_CS_P/N

MGTAVCC_XADC_P/N

MGTAVCC_XADC_CS_P/N

MGTAVTT_XADC_P/N

MGTAVTT_XADC_CS_P/N

NC

ADG707BRU

U14

S1A/B

S2A/B

S3A/B

S4A/B

S5A/B

S6A/B

S7A/B

S8A/B

DA

DB

A[2:0]

ADG707BRU

U13

S1A/B

S2A/B

S3A/B

S4A/B

S5A/B

S6A/B

S7A/B

S8A/B

DA

DB

A[2:0]

GND

1.00 K

1.00 K

FPGA_1V5_SENSE_P

FPGA_1V5_XADC_P

FPGA_1V5_XADC_N

(1.5V Scaled to 0.75V)

GND

3.01 K

1.00 K

VCCO_VADJ_SENSE_P

VCCO_VADJ_XADC_P

VCCO_VADJ_XADC_N

(2.5V Scaled to 0.625V)

GND

3.01 K

1.00 K

FPGA_1V8_SENSE_P

FPGA_1V8_XADC_P

FPGA_1V8_XADC_N

(1.8V Scaled to 0.45V)

GND

1.00 K

1.00 K

MGTAVCC_SENSE_P

MGTAVCC_XADC_P

MGTAVCC_XADC_N

(1.0V Scaled to 0.5V)

GND

1.00 K

1.00 K

MGTAVTT_SENSE_P

MGTAVTT_XADC_P

MGTAVTT_XADC_N

(1.2V Scaled to 0.6V)

GND

3.01 K

1.00 K

FPGA_3V3_SENSE_P

FPGA_3V3_XADC_P

FPGA_3V3_XADC_N

(3.3V Scaled to 0.825V)

Loading...

Loading...