KCU105 Board User Guide www.xilinx.com 38

UG917 (v1.4) September 25, 2015

Chapter 1: KCU105 Evaluation Board Features

Quad 227:

• MGTREFCLK0 - MGT_SI570_CLOCK_C_P/N clock

• MGTREFCLK1 - SI5328_OUT_C_P/N jitter attenuator clock

•Contains four GTH transceivers allocated to FMC_HPC_DP[7:4]_C2M_P/N

Quad 228:

• MGTREFCLK0 - FMC_HPC_GBTCLK0_M2C_C_P/N clock

• MGTREFCLK1 - FMC_HPC_GBTCLK1_M2C_C_P/N clock

• Contains four GTH transceivers allocated to FMC_HPC_DP[3:0]_C2M/M2C_P/N

Tab le 1- 9 lists the GTH banks 224 and 225 interface connections between FPGA U1 and

8-lane PCIe connector P1.

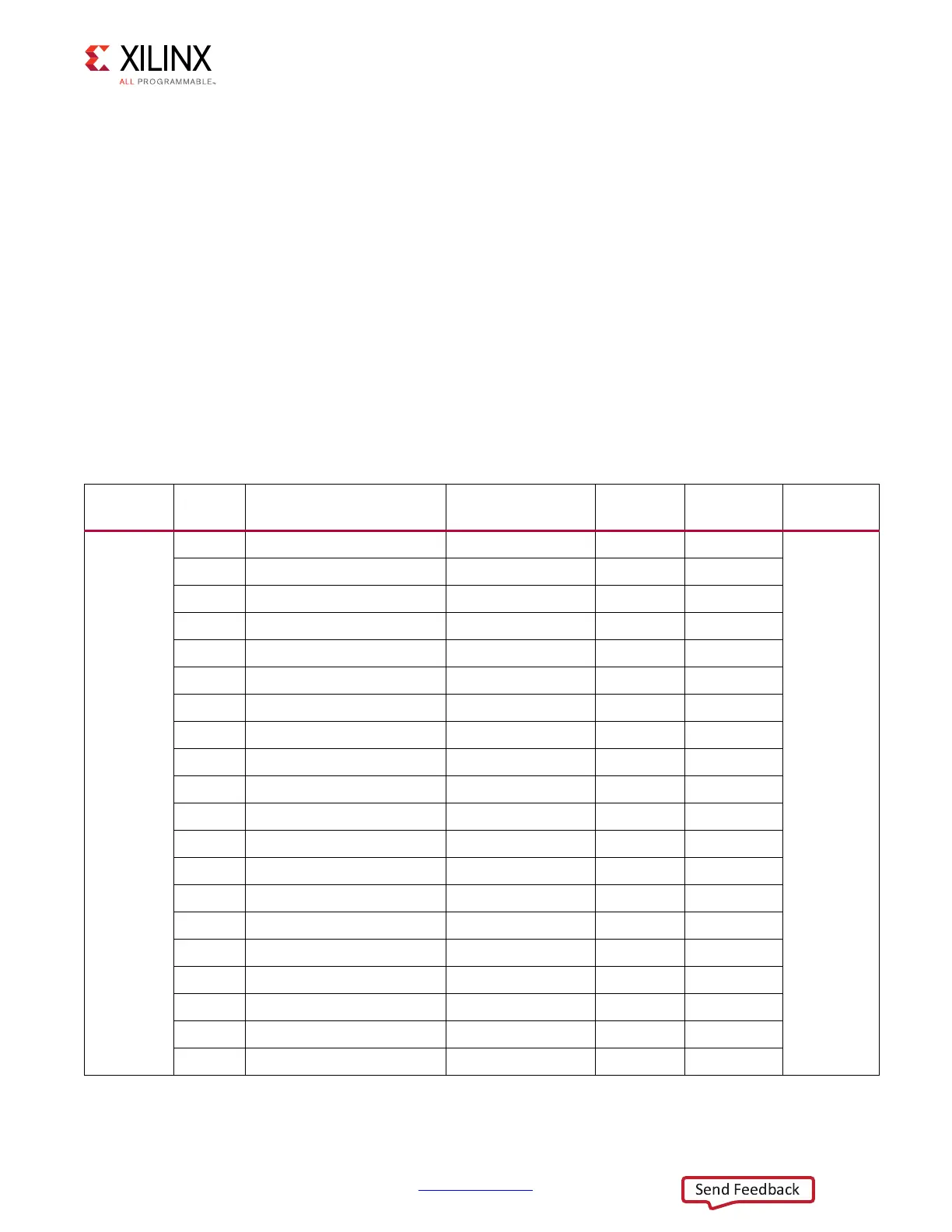

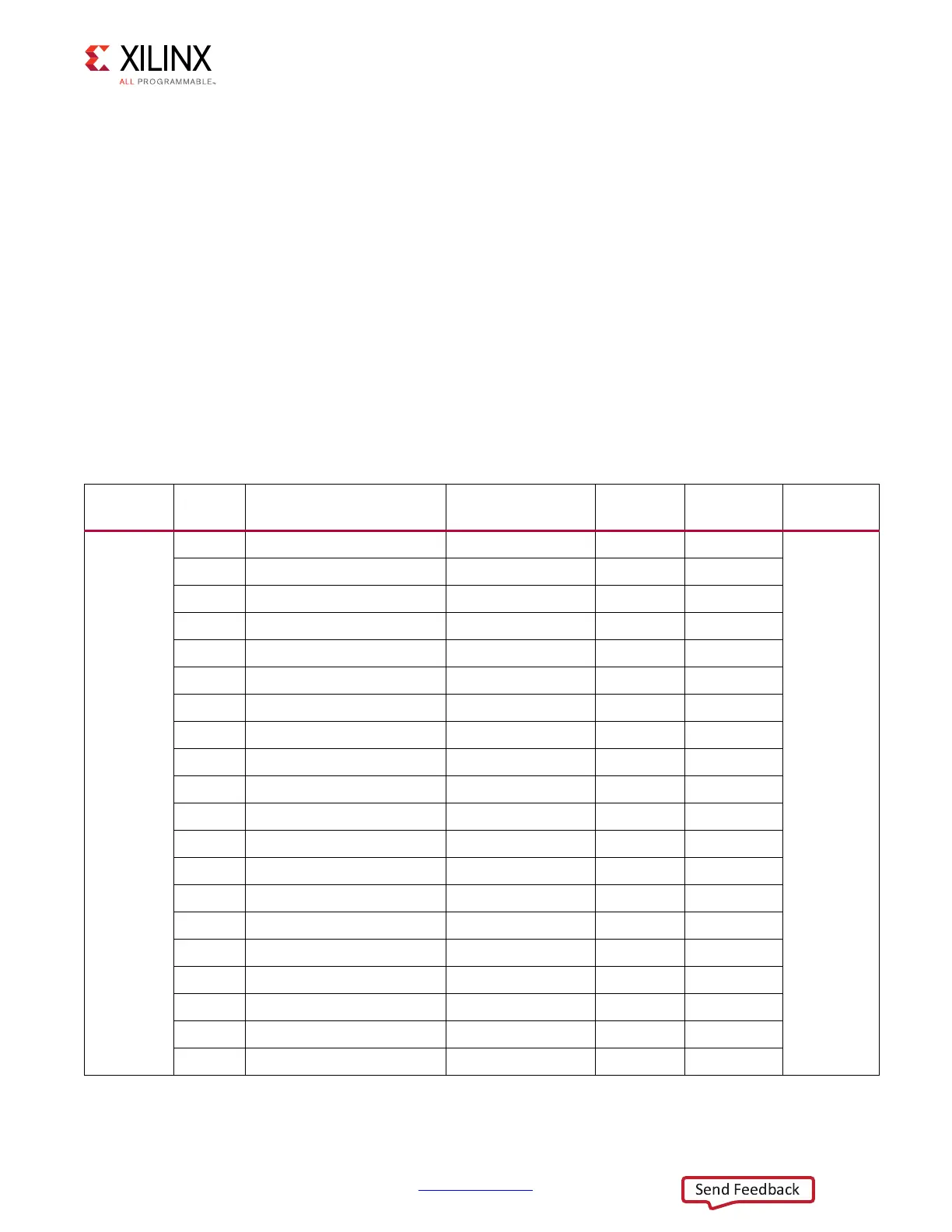

Table 1-9: KCU105 Board FPGA U1 GTH Banks 224 and 225 Connections to PCIe Connector P1

Transceiver

Bank

FPGA

(U1) Pin

FPGA (U1) Pin Name

Schematic Net

Name

Connected

Pin

Connected

Pin Name

Connected

Device

GTH Bank

224

AN4 MGTHTXP0_224 PCIE_TX7_P A47 PERp7

PCIe Edge

Connector

P1

AN3 MGTHTXN0_224 PCIE_TX7_N A48 PERn7

AP2 MGTHRXP0_224 PCIE_RX7_P B45 PETp7

AP1 MGTHRXN0_224 PCIE_RX7_N B46 PETn7

AM6 MGTHTXP1_224 PCIE_TX6_P A43 PERp6

AM5 MGTHTXN1_224 PCIE_TX6_N A44 PERn6

AM2 MGTHRXP1_224 PCIE_RX6_P B41 PETp6

AM1 MGTHRXN1_224 PCIE_RX6_N B42 PETn6

AL4 MGTHTXP2_224 PCIE_TX5_P A39 PERp5

AL3 MGTHTXN2_224 PCIE_TX5_N A40 PERn5

AK2 MGTHRXP2_224 PCIE_RX5_P B37 PETp5

AK1 MGTHRXN2_224 PCIE_RX5_N B38 PETn5

AK6 MGTHTXP3_224 PCIE_TX4_P A35 PERp4

AK5 MGTHTXN3_224 PCIE_TX4_N A36 PERn4

AJ4 MGTHRXP3_224 PCIE_RX4_P B33 PETp4

AJ3 MGTHRXN3_224 PCIE_RX4_N B34 PETn4

AF6 MGTREFCLK0P_224 NC NA NA

AF5 MGTREFCLK0N_224 NC NA NA

AD6 MGTREFCLK1P_224 NC NA NA

AD5 MGTREFCLK1N_224 NC NA NA

Loading...

Loading...