KCU105 Board User Guide www.xilinx.com 65

UG917 (v1.4) September 25, 2015

Chapter 1: KCU105 Evaluation Board Features

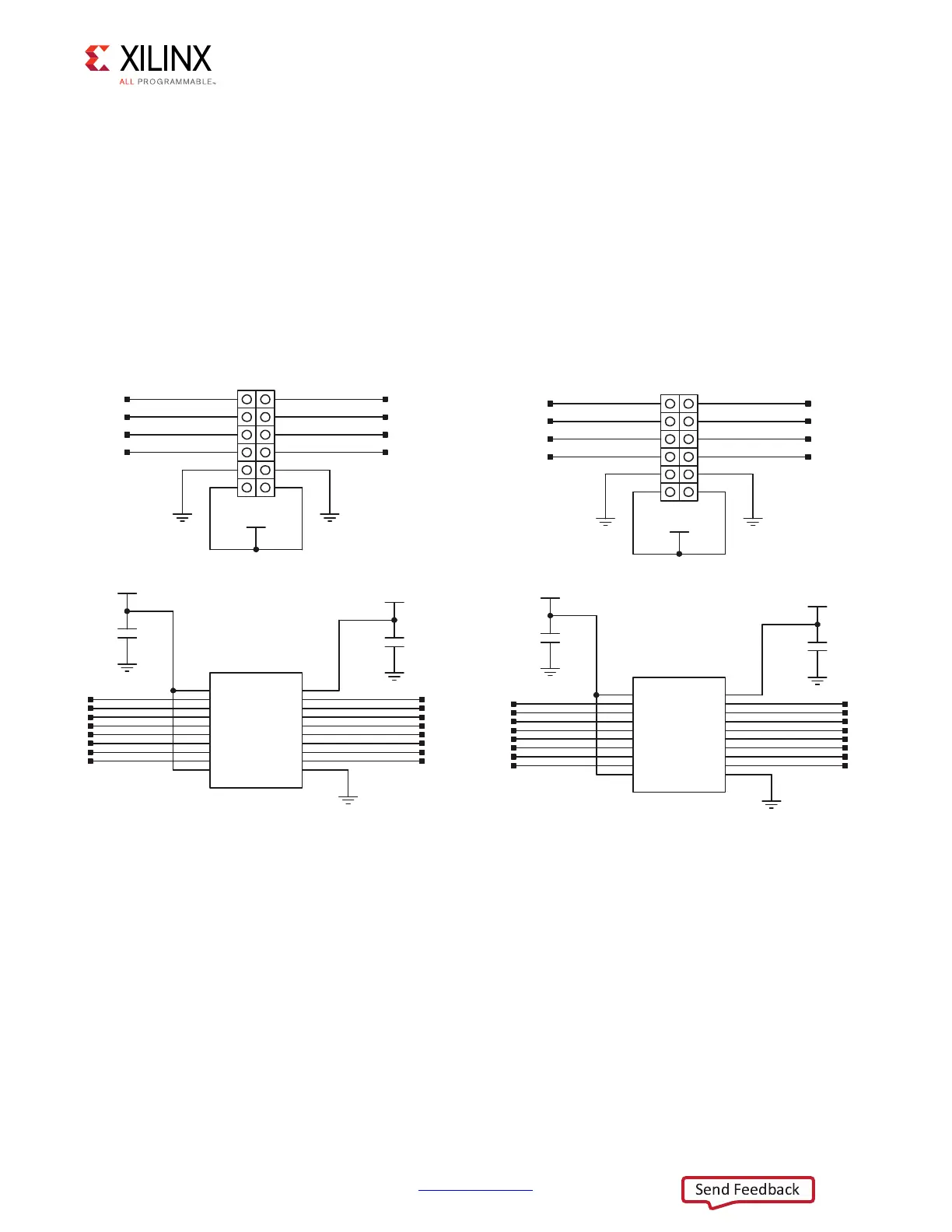

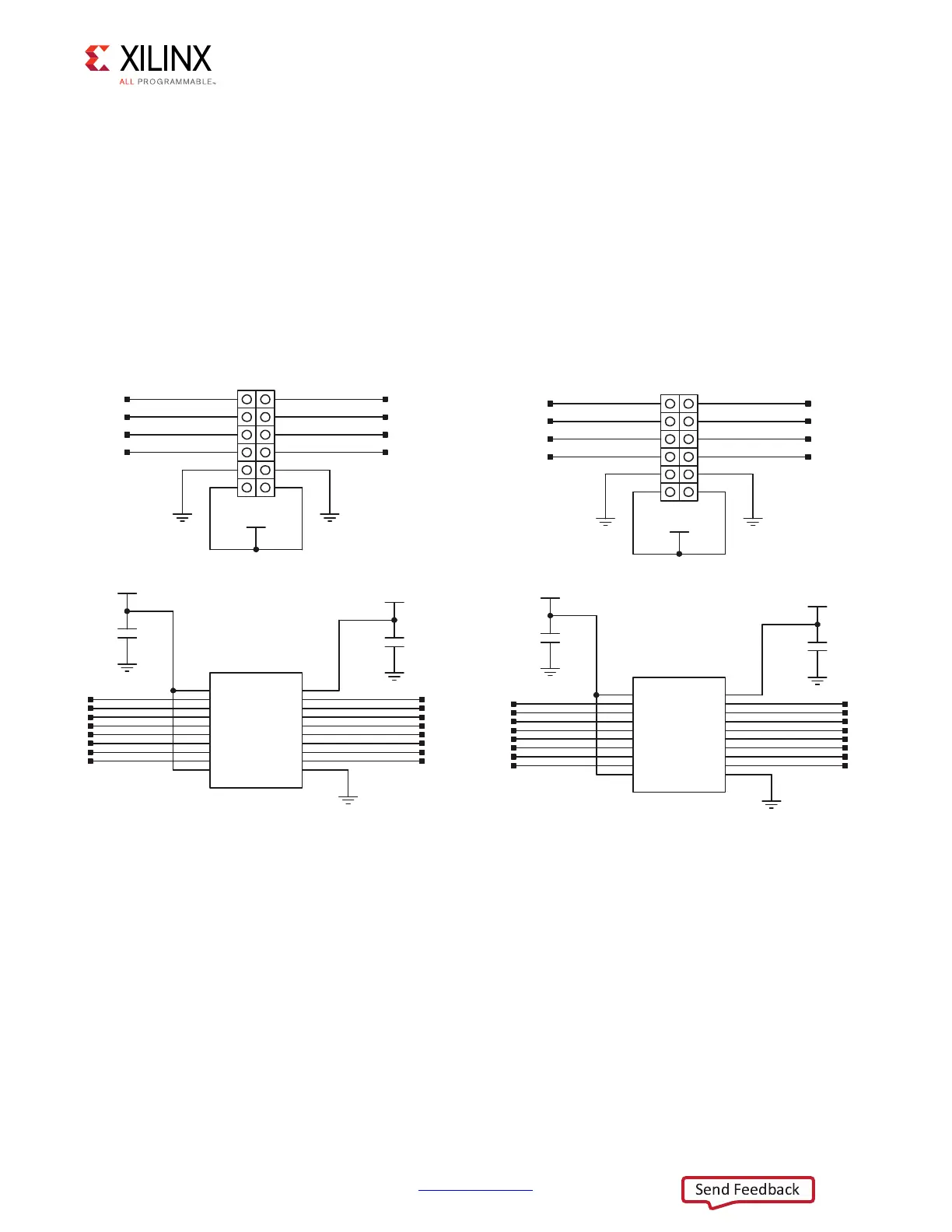

User PMOD GPIO Headers

[Figure 1-2, callout 34]

The KCU105 evaluation board supports two PMOD GPIO headers J52 (right-angle female)

and J53 (vertical male). The PMOD nets connected to these headers are accessed via

level-shifters U41 (PMOD0 J52) and U42 (PMOD1 J53). The level-shifters are wired to the

XCKU040 device U1 banks 44 and 45.

Figure 1-30 shows the GPIO PMOD headers J52 and J53.

X-Ref Target - Figure 1-30

Figure 1-30: PMOD Connectors J52 and J53 with Level-Shifters U42 and U43

*1'

*1'

*1'

*1'*1'

9&&%

%

%

%

%

%

%

*1'

$

$

2(

$

$

$

$

%

$

$

%

9&&$

7;6(

76623B

8

302'BB/6

302'BB/6

302'BB/6

302'BB/6

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'BB/6

302'BB/6

302'BB/6

302'BB/6

*1'

*1'

*1'

*1'*1'

9&&%

%

%

%

%

%

%

*1'

$

$

2(

$

$

$

$

%

$

$

%

9&&$

7;6(

76623B

8

302'BB/6

302'BB/6

302'BB/6

302'BB/6

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'B

302'BB/6

302'BB/6

302'BB/6

302'BB/6

9

8)

&

9

8)

&

9

8)

&

9

8)

&

9&&9B)3*$

9&&9B)3*$

87,/B9

87,/B9

87,/B9

87,/B9

-

+'5B;

-

+'5B;B)B5$

8*BB

9HUWLFDO[

0DOH+HDGHU

5LJKWDQJOH[

)HPDOH+HDGHU

Loading...

Loading...