Spartan-6 FPGA Power Management www.xilinx.com 9

UG394 (v1.1) September 4, 2012

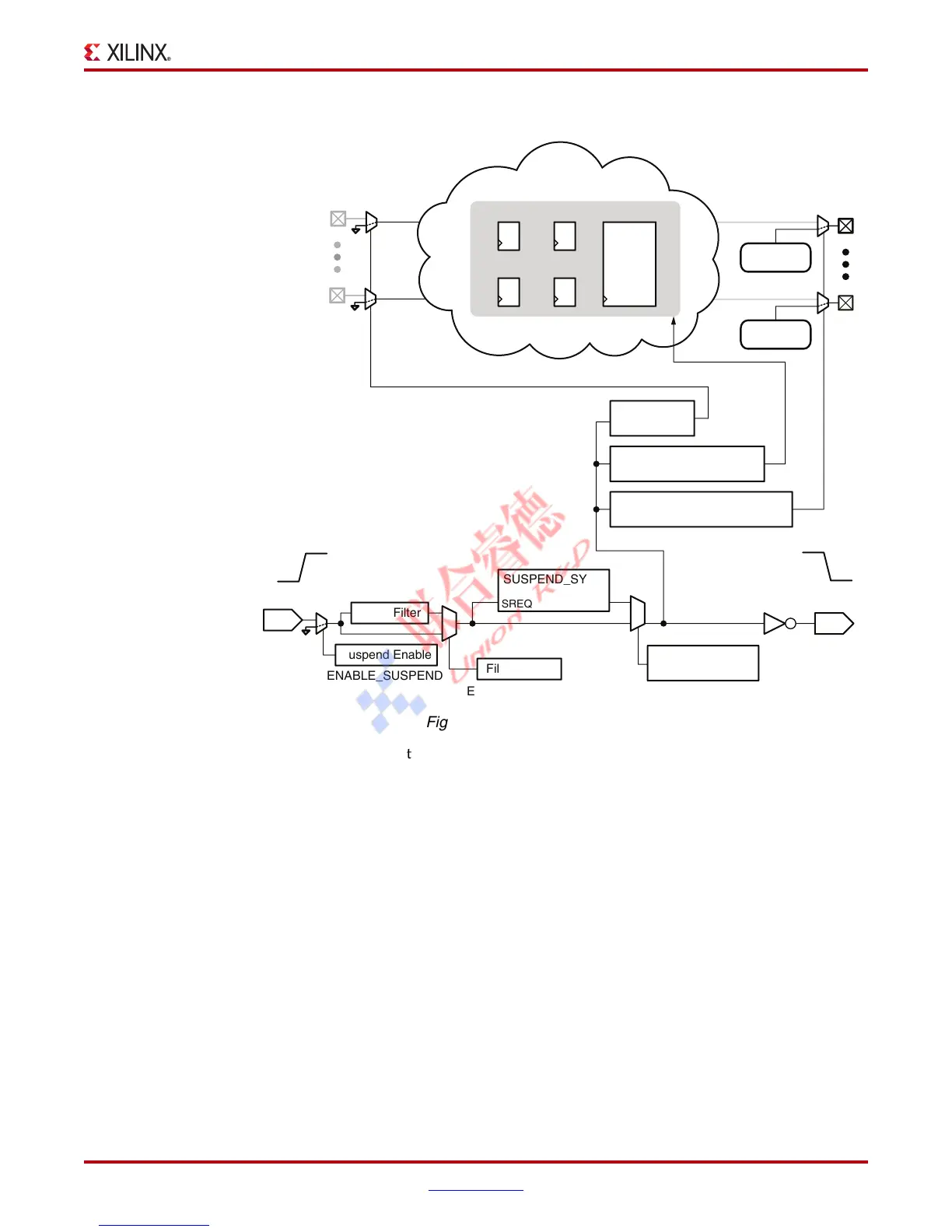

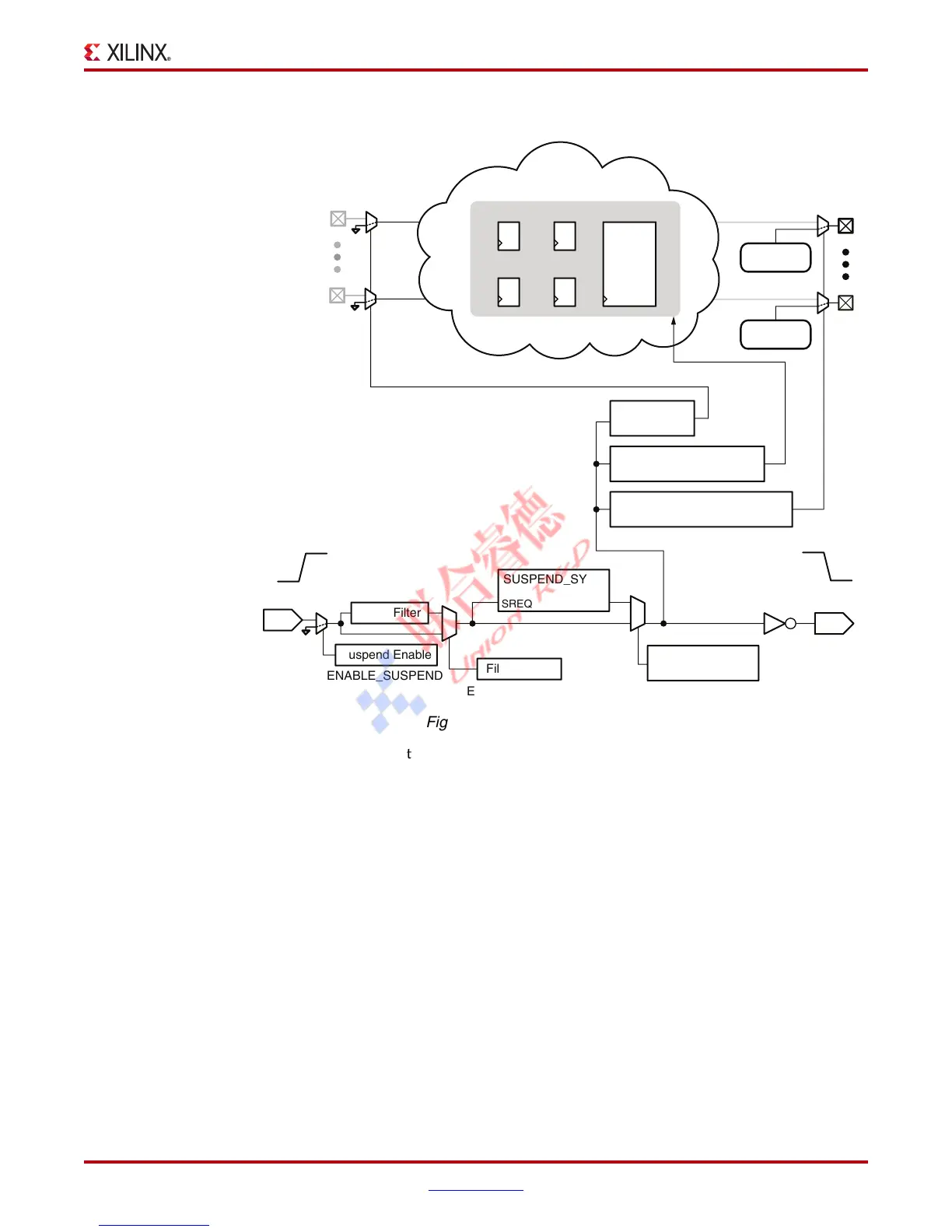

Entering Suspend Mode

The FPGA can only enter suspend mode if enabled in the configuration bitstream (see

Enable the Suspend Feature and Glitch Filtering, page 14). The SUSPEND pin must be Low

during power up and configuration. Once enabled through the bitstream, and the

SUSPEND_SYNC primitive is not present in the design, when the SUSPEND pin is

asserted, the FPGA unconditionally and quickly enters suspend mode.

If the SUSPEND_SYNC primitive is present in the design, the FPGA does not enter

suspend mode until the suspend-acknowledge signal (SACK) is asserted. After the

SUSPEND pin is asserted, the SREQ port of the SUSPEND_SYNC primitive transitions

High. This can be used in the design to initiate any functions that must be completed prior

to the FPGA entering suspend mode. When these functions are complete, drive the SACK

port High.

After the FPGA enters suspend mode, all nonessential FPGA functions are shut down to

minimize power dissipation. The FPGA retains all configuration data while in suspend

mode. After entering suspend mode, all writable clocked primitives are write-protected

against spurious write operations, and all FPGA inputs and interconnects are shut down.

This allows the design state to be held static during suspend mode. If a specific design state

must be maintained, see Design Requirements to Maintain Application Data, page 17.

X-Ref Target - Figure 1-1

Figure 1-1: Entering Suspend Mode

SUSPEND

Attribute

SUSPEND

Attribute

Glitch Filter

Suspend Enable

SRL

LUT RAM

Flip-Flops

Latches

Block RAM

Writable Clocked Primitives

FPGA Application Logic

FPGA

Inputs

FPGA

Outputs

SUSPEND

AWAK

E

ENABLE_SUSPEND

ENABLE_SUSPEND

Filter Select

Write-Protect Writable

Clocked Primitives

Apply SUSPEND Attribute

to FPGA Outputs

Block FPGA

Inputs

SUSPEND_SYNC

SUSPEND_SYNC

Instantiated

UG394_c1_01_020310

SREQ SACK

Loading...

Loading...