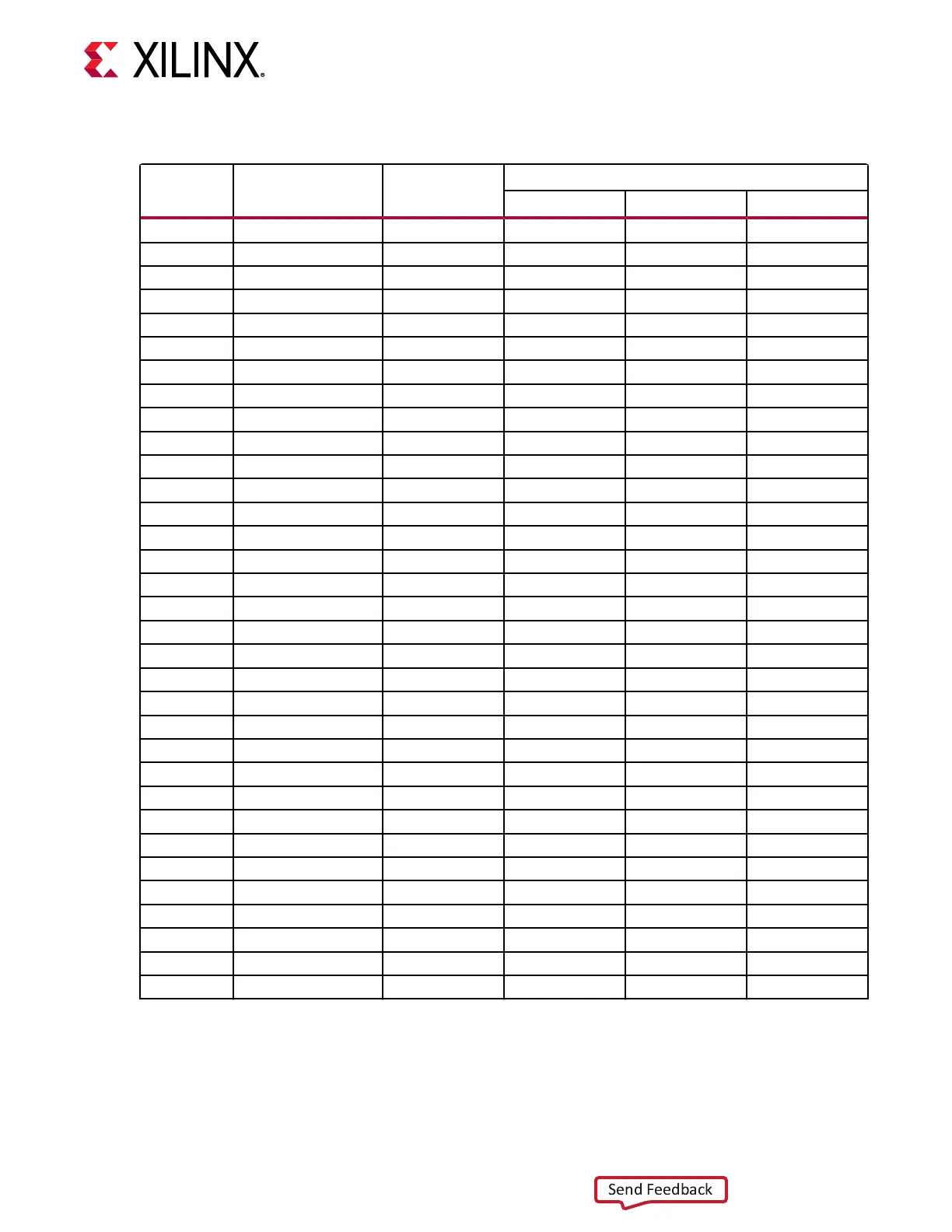

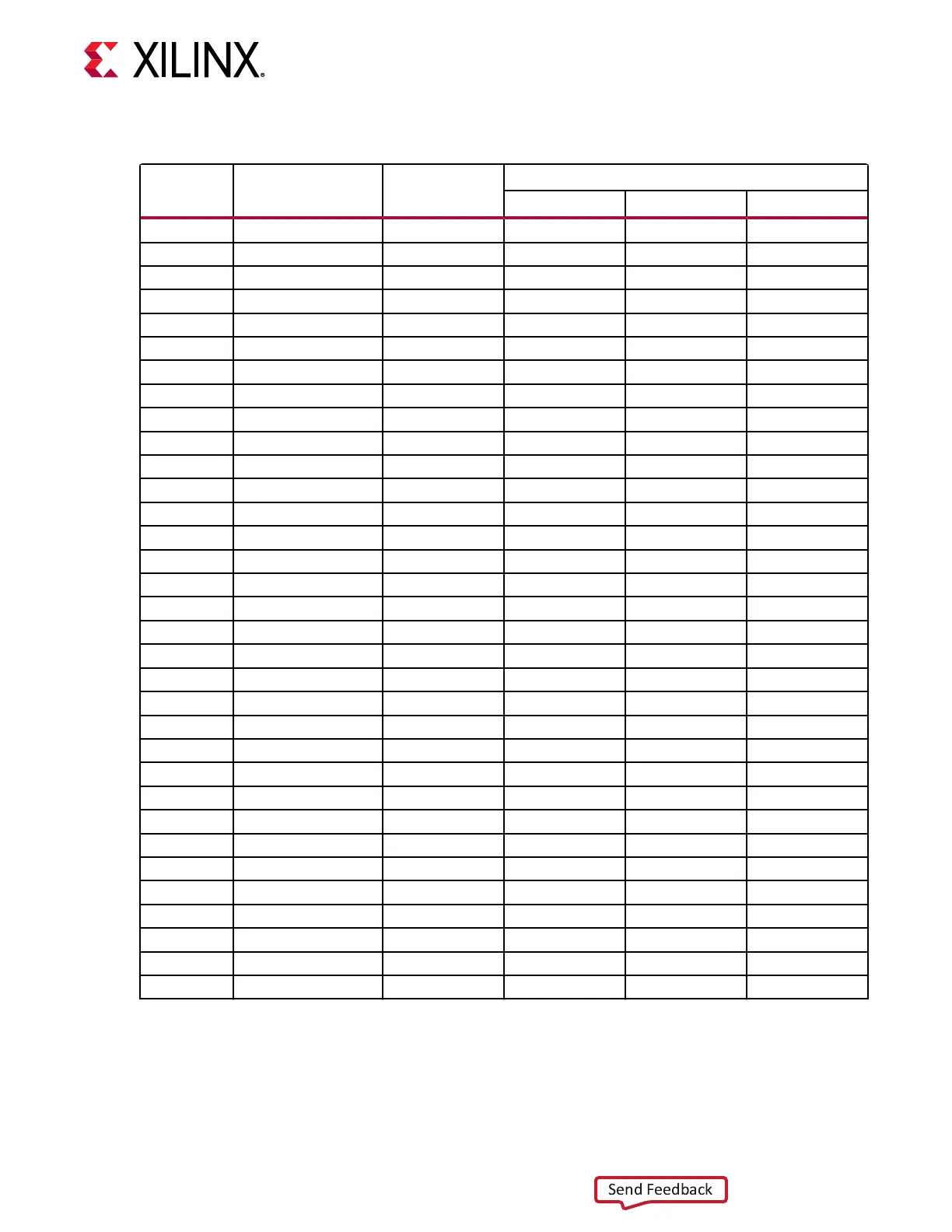

Table 7: RLD3 Memory 72-bit I/F to FPGA U1 Banks 73, 74, and 75 (cont'd)

FPGA (U1)

Pin

Schematic Net

Name

I/O Standard

Component Memory

Pin # Pin Name Ref. Des.

E34 RLD3_72B_REF_B SSTL12 F8 REF_B U37, U39

G37 RLD3_72B_CK_P SSTL12 H7 CK U37, U39

F38 RLD3_72B_CK_N SSTL12 G7 CK_B U37, U39

D35 RLD3_72B_RESET_B SSTL12 A13 RESET_B U37, U39

A34 RLD3_72B_CS_B SSTL12 E12 CS_B U37, U39

H37 RLD3_72B_DK0_P DIFF_SSTL12 D7 DK0 U39

H38 RLD3_72B_DK0_N DIFF_SSTL12 C7 DK0_B U39

H34 RLD3_72B_DK1_P DIFF_SSTL12 K7 DK1 U39

H35 RLD3_72B_DK1_N DIFF_SSTL12 L7 DK1_B U39

G38 RLD3_72B_DK2_P DIFF_SSTL12 D7 DK0 U37

F39 RLD3_72B_DK2_N DIFF_SSTL12 C7 DK0_B U37

G35 RLD3_72B_DK3_P DIFF_SSTL12 K7 DK1 U37

G36 RLD3_72B_DK3_N DIFF_SSTL12 L7 DK1_B U37

L33 RLD3_72B_QK0_P DIFF_SSTL12 D9 QK0 U39

K33 RLD3_72B_QK0_N DIFF_SSTL12 E8 QK0_B U39

H33 RLD3_72B_QK1_P DIFF_SSTL12 K9 QK1 U39

G33 RLD3_72B_QK1_N DIFF_SSTL12 J8 QK1_B U39

E31 RLD3_72B_QK2_P DIFF_SSTL12 D5 QK2 U39

E32 RLD3_72B_QK2_N DIFF_SSTL12 E6 QK2_B U39

C30 RLD3_72B_QK3_P DIFF_SSTL12 K5 QK3 U39

B31 RLD3_72B_QK3_N DIFF_SSTL12 J6 QK3_B U39

K41 RLD3_72B_QK4_P DIFF_SSTL12 D9 QK0 U37

K42 RLD3_72B_QK4_N DIFF_SSTL12 E8 QK0_B U37

J44 RLD3_72B_QK5_P DIFF_SSTL12 K9 QK1 U37

H44 RLD3_72B_QK5_N DIFF_SSTL12 J8 QK1_B U37

E42 RLD3_72B_QK6_P DIFF_SSTL12 D5 QK2 U37

E43 RLD3_72B_QK6_N DIFF_SSTL12 E6 QK2_B U37

F40 RLD3_72B_QK7_P DIFF_SSTL12 K5 QK3 U37

F41 RLD3_72B_QK7_N DIFF_SSTL12 J6 QK3_B U37

F30 RLD3_72B_QVLD0 SSTL12 J12 QVLD0 U39

E28 RLD3_72B_QVLD1 SSTL12 J2 QVLD1 U39

D45 RLD3_72B_QVLD2 SSTL12 J12 QVLD0 U37

A44 RLD3_72B_QVLD3 SSTL12 J2 QVLD1 U37

The VCU128 RLD3 72-bit memory component interface adheres to the constraints guidelines

documented in the "RLD3 Design Guidelines" secon of the UltraScale Architecture-Based FPGAs

Memory IP LogiCORE IP Product Guide (PG150). The VCU128 RLD3 memory component interface

is a 40Ω impedance implementaon.

Chapter 3: Board Component Descriptions

UG1302 (v1.0) December 21, 2018 www.xilinx.com

VCU128 Board User Guide 28

Loading...

Loading...