28 www.xilinx.com Virtex-5 FPGA ML561 User Guide

UG199 (v1.2.1) June 15, 2009

Chapter 3: Hardware Description

R

200 MHz LVPECL Clock

The 200 MHz LVPECL clock source is an Epson EG-2121CA200M-PCHS oscillator (Y1)

with a differential output. The oscillator runs at 200 MHz ± 100 PPM with an operating

voltage of 2.5V ±5%. This output is fed into an ICS853006 LVPECL buffer for generating a

separate differential copy for each FPGA as well as a test point (P59).

SMA Clock

Two SMA connectors are provided for the input of an off-board differential clock (J19 and

J20). A differential clock buffer (ICS853006) is used on the board (U17 and U18) to generate

four LVPECL copies of the differential clock signal, one for each FPGA along with a probe

point (P40) for testing. The traces from the buffer are routed as a differential pair to each

FPGA where they are terminated with 100Ω differential termination.

33 MHz Clock

A single-ended 33 MHz Epson SG-8002CA oscillator is provided on the board (Y2) for

testing purposes. Four copies of this clock are generated using a clock buffer (ICS8304) on

the board, one per FPGA along with a probe point for testing (P41).

The application using this clock source as an input to the PLL on the Virtex-5 device has

not yet been fully verified.

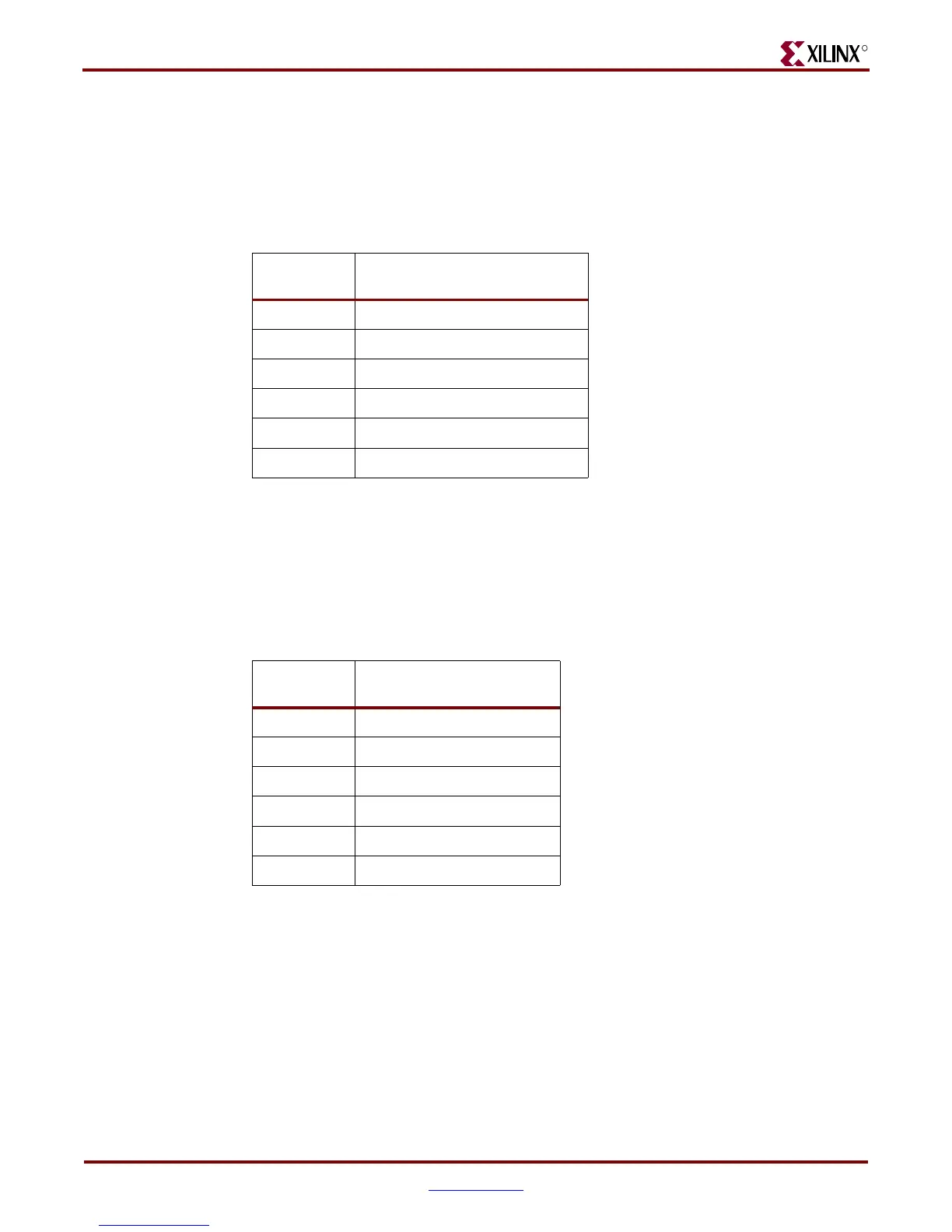

Table 3-10: FPGA 200 MHz IDELAY Reference Clock Source

FPGA # Signal Name

1 DIRECT_CLK_TO_FPGA1_P

1 DIRECT_CLK_TO_FPGA1_N

2 DIRECT_CLK_TO_FPGA2_P

2 DIRECT_CLK_TO_FPGA2_N

3 DIRECT_CLK_TO_FPGA3_P

3 DIRECT_CLK_TO_FPGA3_N

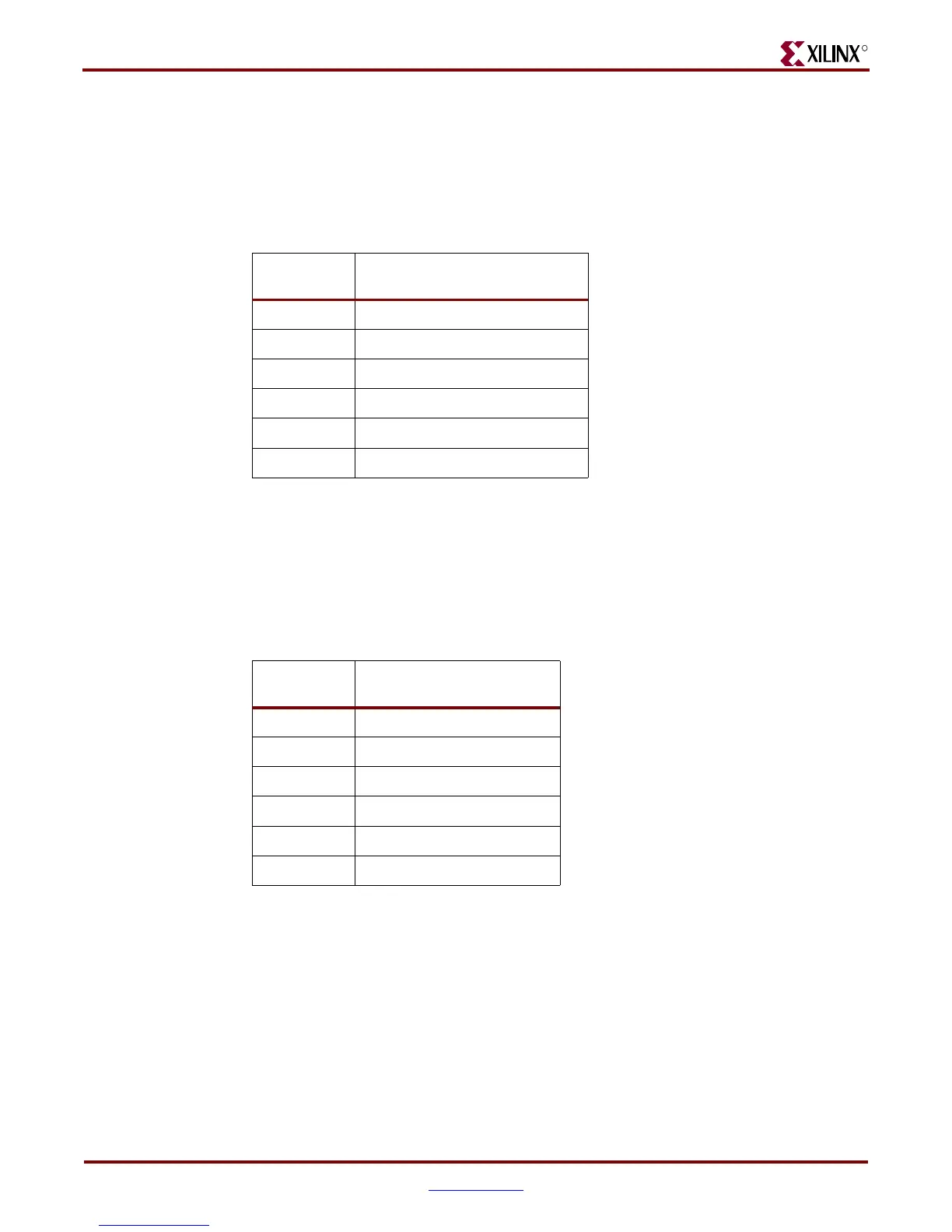

Table 3-11: FPGA External Clock Sources

FPGA # Signal Name

1 EXT_CLK_TO_FPGA1_P

1 EXT_CLK_TO_FPGA1_N

2 EXT_CLK_TO_FPGA2_P

2 EXT_CLK_TO_FPGA2_N

3 EXT_CLK_TO_FPGA3_P

3 EXT_CLK_TO_FPGA3_N

Loading...

Loading...