80 www.xilinx.com Virtex-5 FPGA ML561 User Guide

UG199 (v1.2.1) June 15, 2009

Chapter 7: ML561 Hardware-Simulation Correlation

R

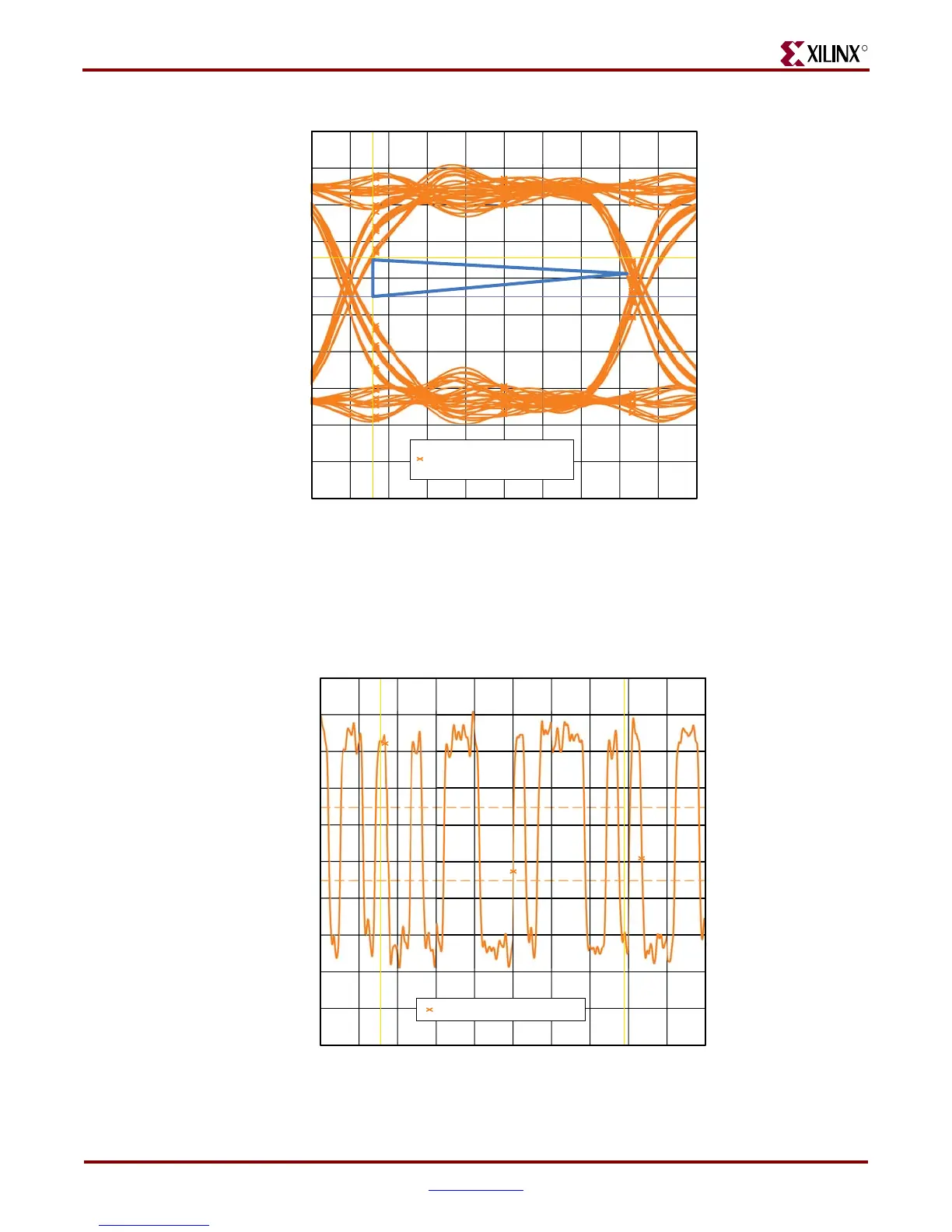

Figure 7-37: DDR2 DIMM Read Extrapolation - Eye Scope Shot at Receiver IOB (Fast Corner)

400.0 800.0 1200.0 1600.0 2000.0 2400.0

-200.0

0.000

200.0

400.0

600.0

800.0

1000.0

1200.0

1400.0

1600.0

1800.0

Time (ps)

Voltage (mV)

UG199_c7_37_071007

Probe 6:U5_B00.H29 (at die)

♦ 333 MHz, Fast, PRBS6, 83% UI

♦ Cursor 1: 697.0 mV, 763.0 ps

♦ Cursor 2: 776.6 mV, 2.0052 ns

♦ Delta Voltage = 79.5 mV, Delta Time = 1.2422 ns (83% UI)

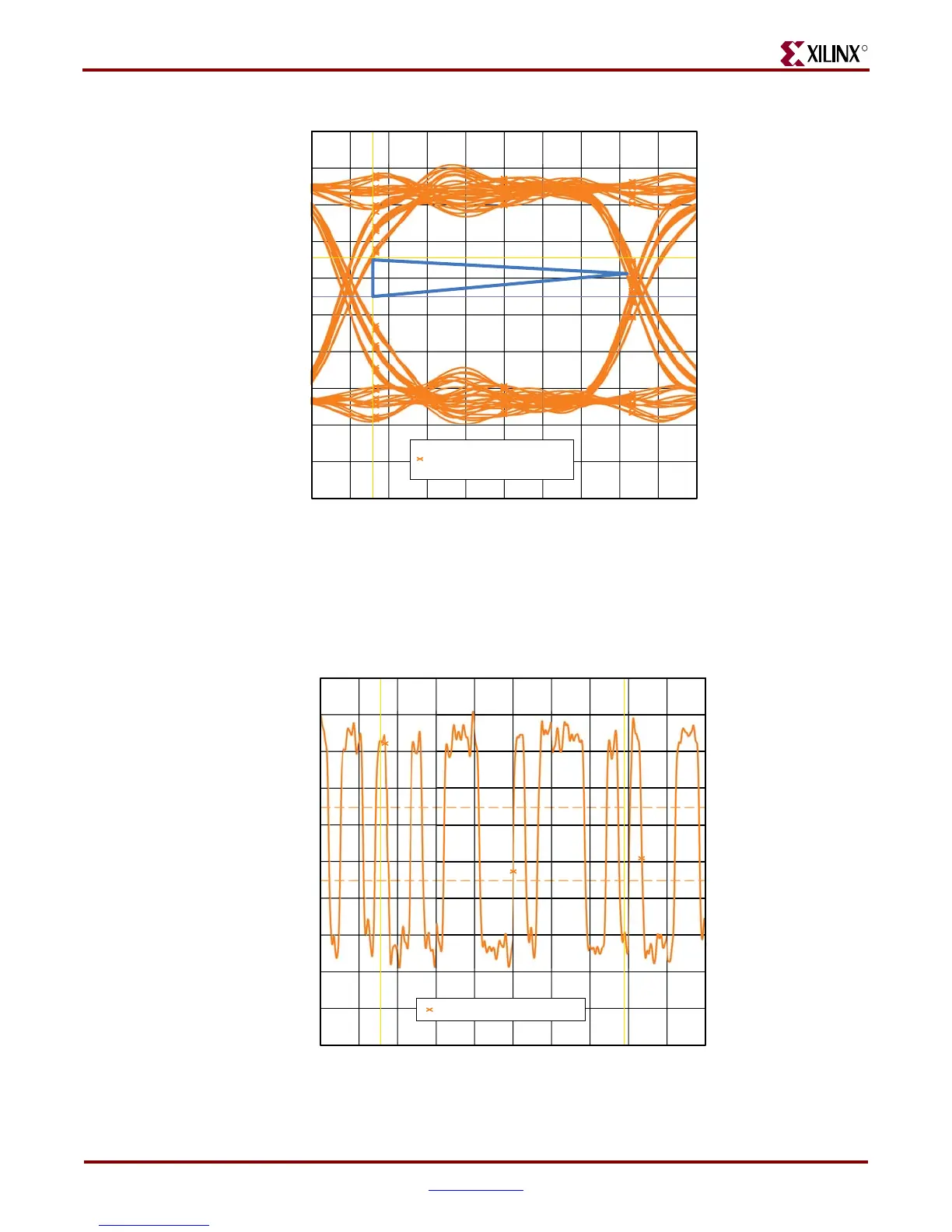

Figure 7-38: DDR2 DIMM Read Extrapolation - Waveform Scope Shot at Receiver IOB (Fast Corner)

30.000 40.000 50.000 60.000 70.000

-200.0

0.000

200.0

400.0

600.0

800.0

1000.0

1200.0

1400.0

1600.0

1800.0

UG199_c7_38_071007

Time (ns)

Voltage (mV)

Probe 6:U5_B00.H29 (at die)

Loading...

Loading...