ZCU102 Evaluation Board User Guide www.xilinx.com 90

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

The GTR selections provided with GT switch topology shown in Figure 3-37 are:

1. PCIe Gen2/1 x4

2. DisplayPort (2-Lanes), USB, SATA

3. PCIe Gen2/1 x2, USB, SATA

4. PCIe Gen2/1 x1, DisplayPort (1-Lane), USB, SATA

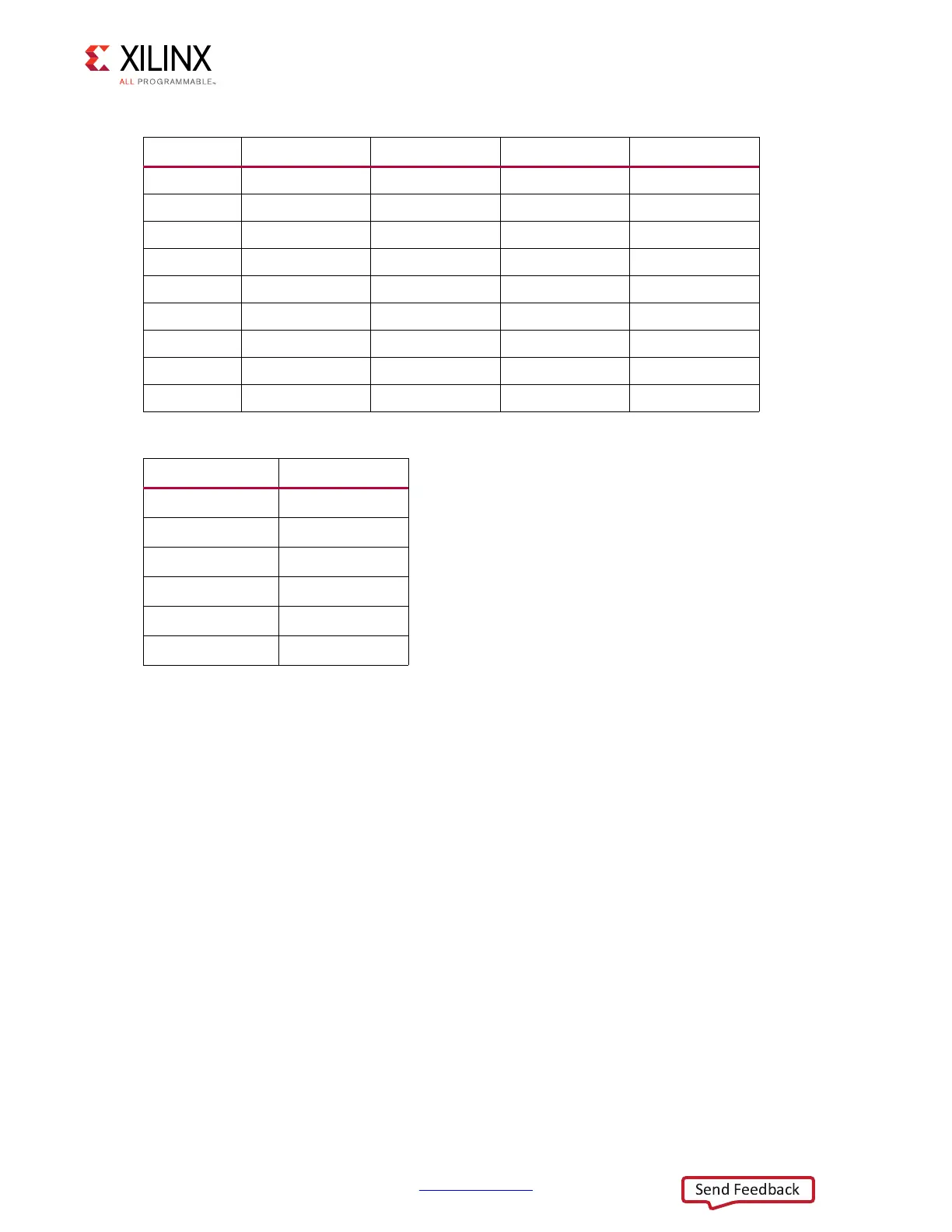

Table 3-41: XCZU9EG Interconnect Matrix

Protocol PHY Lane 0 PHY Lane 1 PHY Lane 2 PHY Lane 3

PCIe

PCIe.0 PCIe.0 PCIe.0 PCIe.0

SATA

SATA.0 SATA.1 SATA.0 SATA.1

USB0

USB0 USB0 USB0

USB1

USB1

DisplayPort

DP.1 DP.0 DP.1 DP.0

SGMII0

SGMII0

SGMII1

SGMII1

SGMII2

SGMII2

SGMII3

SGMII3

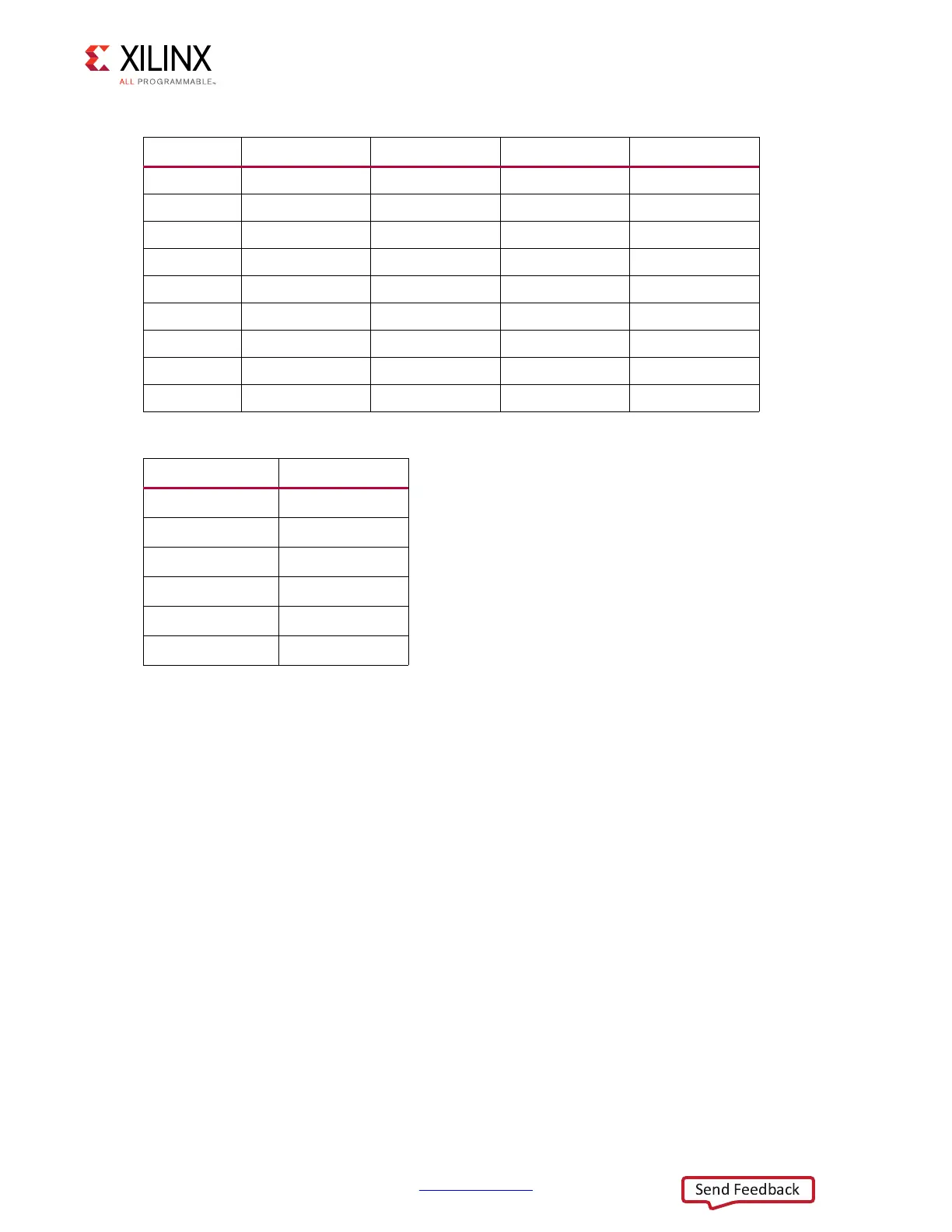

Table 3-42: Interconnect Matrix Settings and GTR Lane Functionality

Protocol Values

Power down

3’h0

PCIe

3’h1

SATA

3’h2

USB

3’h3

DisplayPort

3’h4

SGMII

3’h5

Loading...

Loading...