GPIO (MIO 13, 38)

These two GPIO bits are connected to the U38 MSP430 system controller for general purpose

signaling or communicaons between the Zynq UltraScale+ RFSoC and the MSP430 system

controller. These signals are level-shied by TSX0108E U37. The connecons between the U38

system controller and the ZU48DR RFSoC are listed in following table.

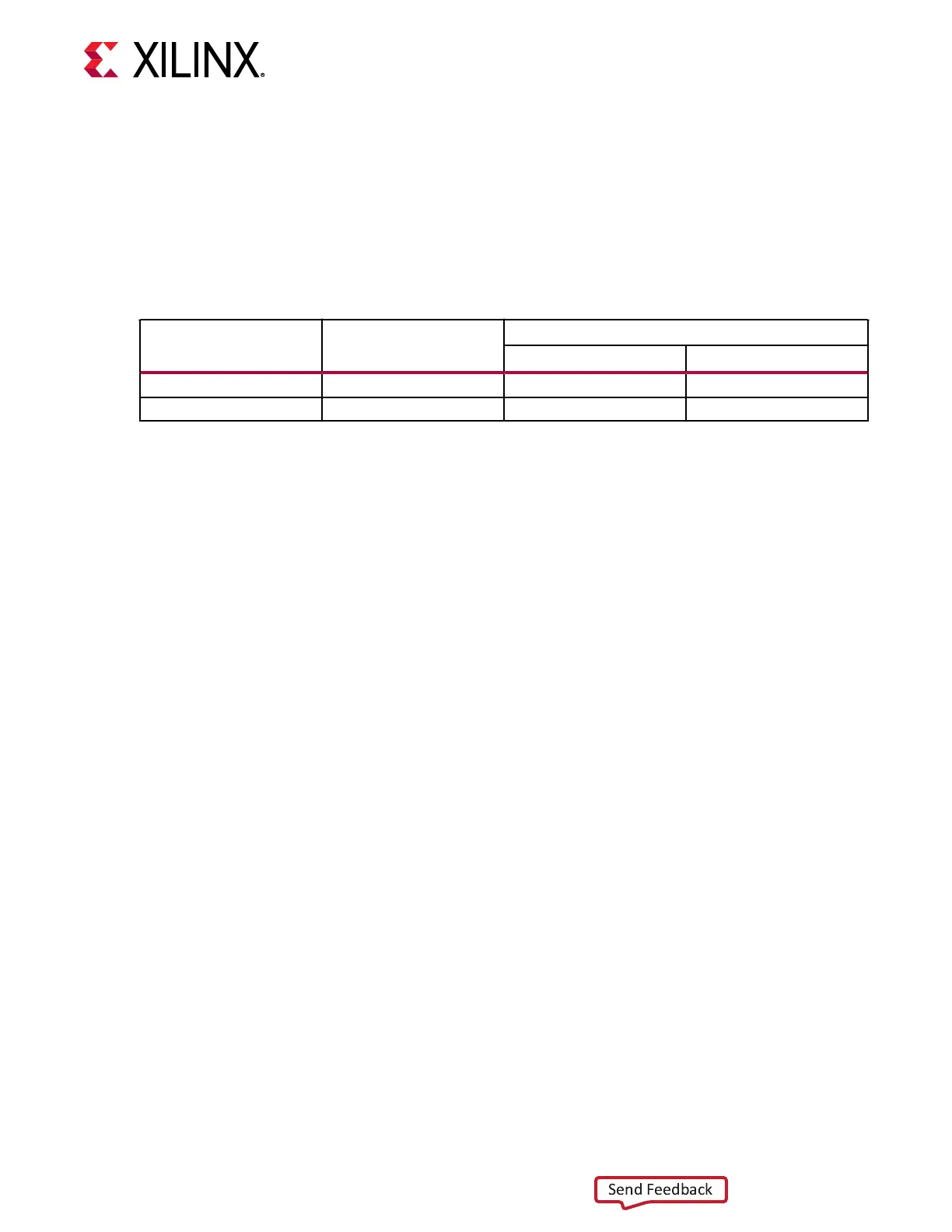

Table 8: System Controller U38 GPIO Connections to ZU48DR U1

ZU48DR U1 Pin Net Name

MSP430 U38

Pin Name Pin Number

G32 MIO38_PS_GPIO1 P1_6 19

AU26 MIO13_PS_GPIO2 P1_7 20

I2C Bus Topology Overview

I2C0 (MIO 14-15), I2C1 (MIO 16-17)

The following gure shows a high-level view of the I2C0 and I2C1 bus connecvity.

Chapter 3: Board Component Descriptions

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 29

Loading...

Loading...