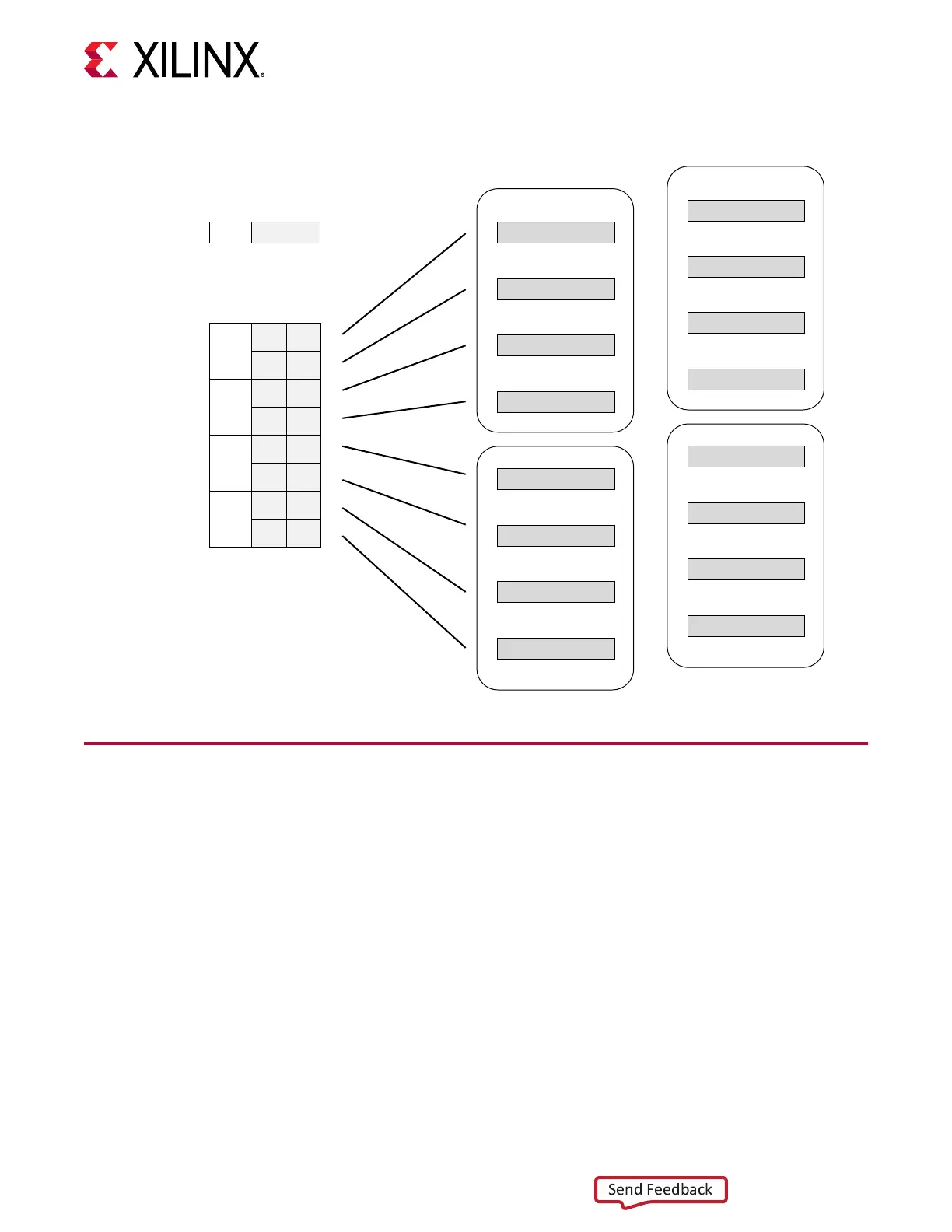

Figure 28: DAC 16 Lanes

228229230231

0

2

1

3

0

2

1

3

0

2

1

3

0

2

1

3

Tile Channel

DAC228_T0_CH1

DAC228_T0_CH3

DAC229_T1_CH1

DAC229_T1_CH3

JHC2

DAC228_T0_CH0

DAC228_T0_CH2

DAC229_T1_CH0

DAC229_T1_CH2

JHC1

DAC230_T2_CH1

DAC230_T2_CH3

DAC231_T3_CH1

DAC231_T3_CH3

JHC4

DAC230_T2_CH0

DAC230_T2_CH2

DAC231_T3_CH0

DAC231_T3_CH2

JHC3

DAC

X24155-062520

Features

The XM655 balun add-on card uses the 8 x 50 x 2 female LPAM-50-01.0-L-08-2-K-TR

connectors and pinout as dened in XM650/655 Connector Pinout. For signal break-out Carlisle

CoreHC2 connectors and cable assemblies are used. Digital I/O and I2C are supported on

headers.

The XM655 module features are:

• 8 ADC dierenal signals to 4 male Carlisle CoreHC2 connector pads

• 8 DACs dierenal signals to 4 male Carlisle CoreHC2 connector pads

• 2 ADC inputs – compression mount SMAs through low frequency baluns – Minicircuits

TCM2-33WX+

• 2 ADC inputs – compression mount SMAs through mid frequency baluns – Anaren

BD1631J50100AHF

Appendix C: HW-XM650/655 Balun Daughter Cards for Gen 3 RFSoC EVM

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 75

Loading...

Loading...