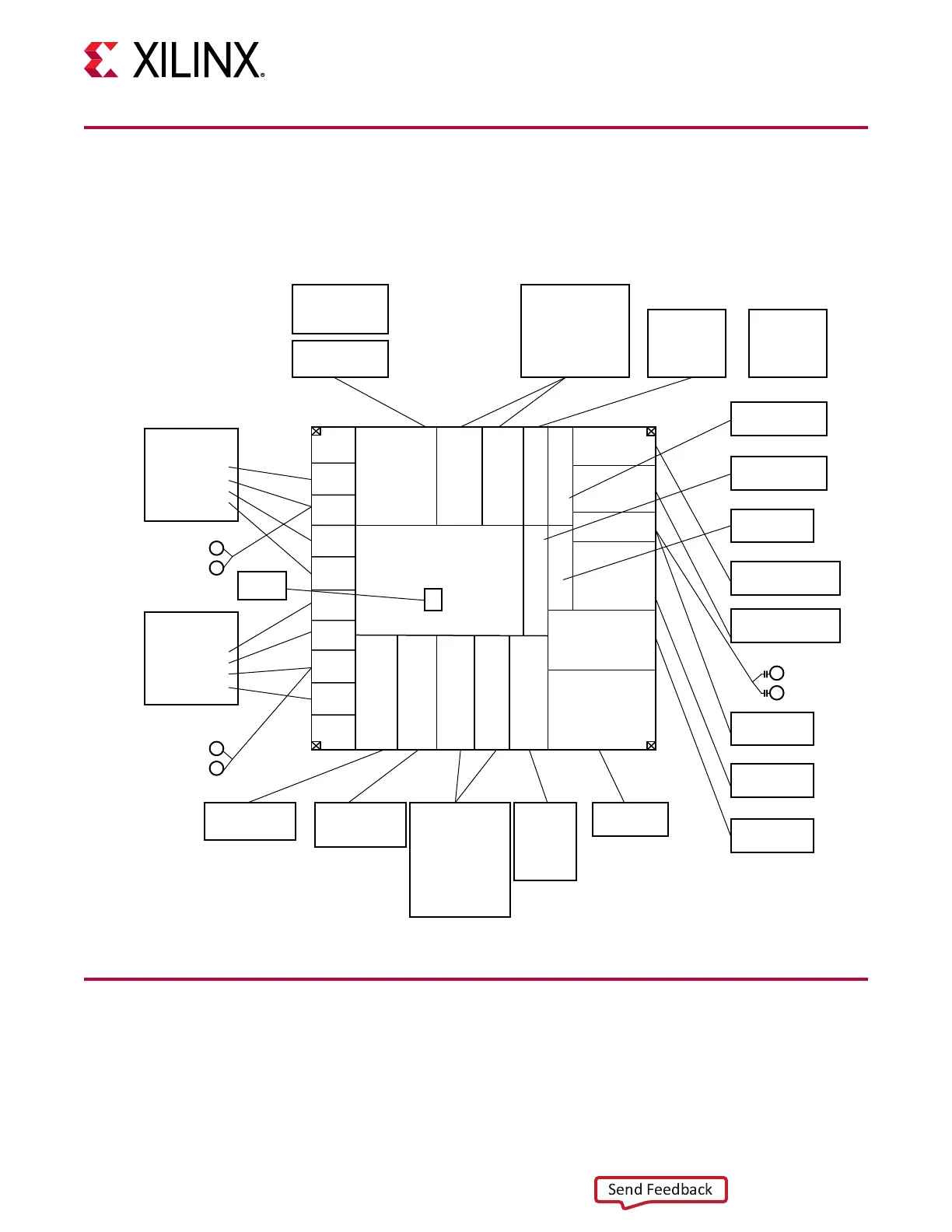

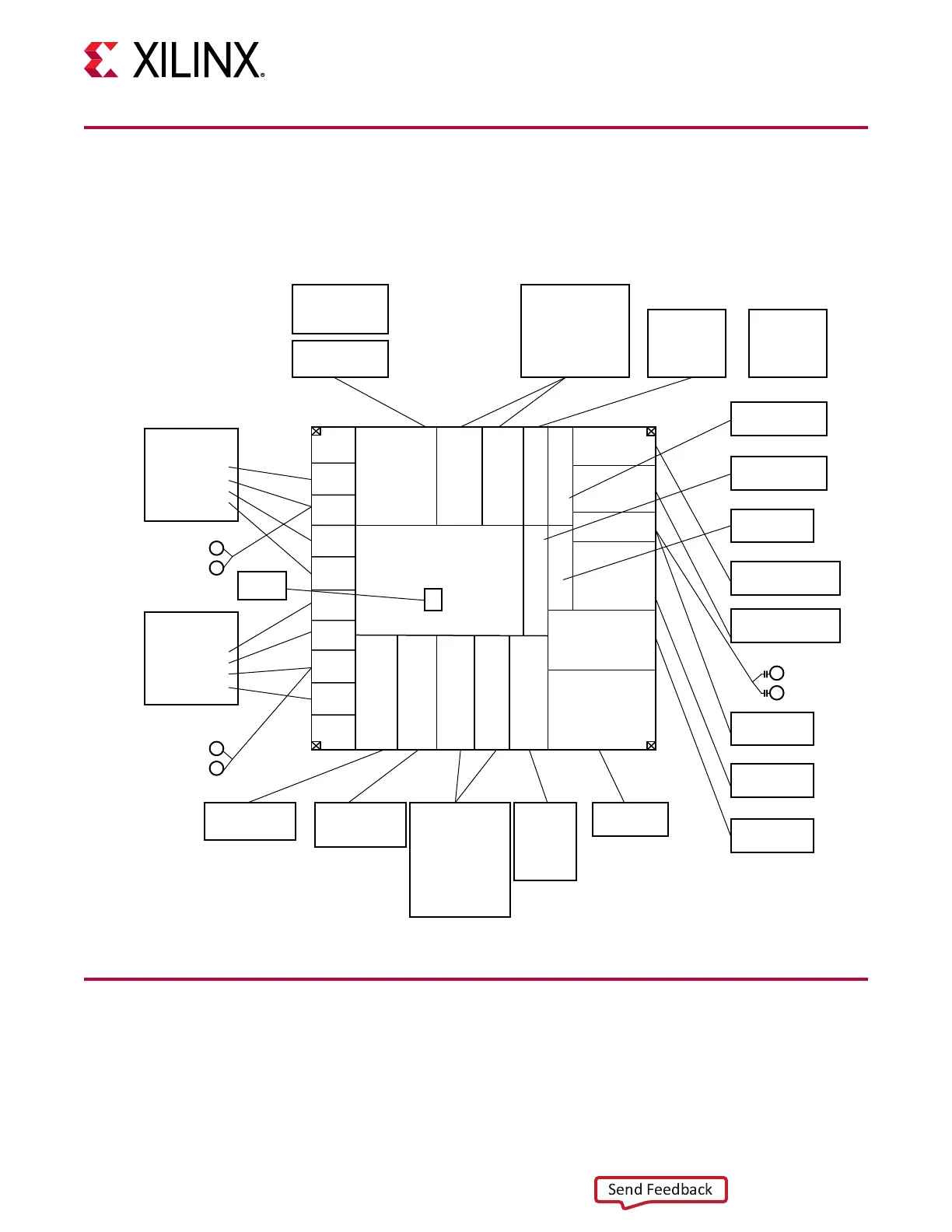

Block Diagram

A block diagram of the ZCU208 evaluaon board is shown in the following gure.

Figure 1: Evaluation Board Block Diagram

RFMC CONN. 2

DAC_T3_CH[0,2]

DAC_T2_CH[0,2]

DAC_T1_CH[0,2]

DAC_T0_CH[0,2]

SYSMON

Header

RFMC CONN. 1

ADC_T3_CH[0,2]

ADC_T2_CH[0,2]

ADC_T1_CH[0,2]

ADC_T0_CH[0,2]

FMCP HSPC

LA[00:16]

FMCP HSPC Sync

GPIO_SW

MSP430

System

Controller

DDR4 Component

32-bit (4x8-bit)

C1 Interface

GPIO_DIP_SW[0:1]

8A34001_GPIO[0:7]

8A34001_GPIO[10:15]

PL_I2C0

PL_I2C1

CLK104 CONN. Banks

67.68.84.87.226.228

SD 3.0

PS_PMU_GPO[0:5]

USB0 3.0

ETHERNET RGMII

CONFIG. IF

JTAG IF

SFP[2:3]

SFP[0:1]

USB0 3.0

SATA1 M.2

DDR4 SODIMM

64-bit

PS PB/LED

UART0

PS_I2C0

PS_12C1

QSPI LWR

QSPI UPR

DDR4 Component

32-bit (4x8-bit)

C0 Interface

GPIO_LED

MPS430_GPIO

SFP[0:3]_TX_DISABLE

UART2

MSP430_UCA1

ADCIO

GPIO_DIP_SW[6:7]

CPU_RESET

FMCP HSPC

LA[17:33]

GPIO_DIP_SW[2:3[

FMCP_HSPC_DP[4:7]

FMCP_HSPC_DP[0:3]

DACIO[00:15]

USER_MGT_CLK

(SMA)

ADC_CLK (SMA)

DAC_CLK (SMA)

DAC

CLK

DAC

231

DAC

230

DAC

229

DAC

228

ADC

227

ADC

226

ADC

225

ADC

224

ADC

CLK

84 64 65 66

PS

500

PS DDR 504

XCZU48DR-2FSVG1517

0

87

69 68

67

PS 501

PS 502

PS 503

MGTY

131

MGTY

130

MGTY

129

MGTY

128

PS GTR

505

X23790-040220

Board Features

The ZCU208 evaluaon board features are listed here. Detailed informaon for each feature is

provided in Chapter 3: Board Component Descripons.

Chapter 1: Introduction

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 6

Loading...

Loading...