Clock Generation

The ZCU208 board provides xed and variable clock sources for the ZU48DR Zynq UltraScale+

RFSoC. The following table lists the source devices for each clock.

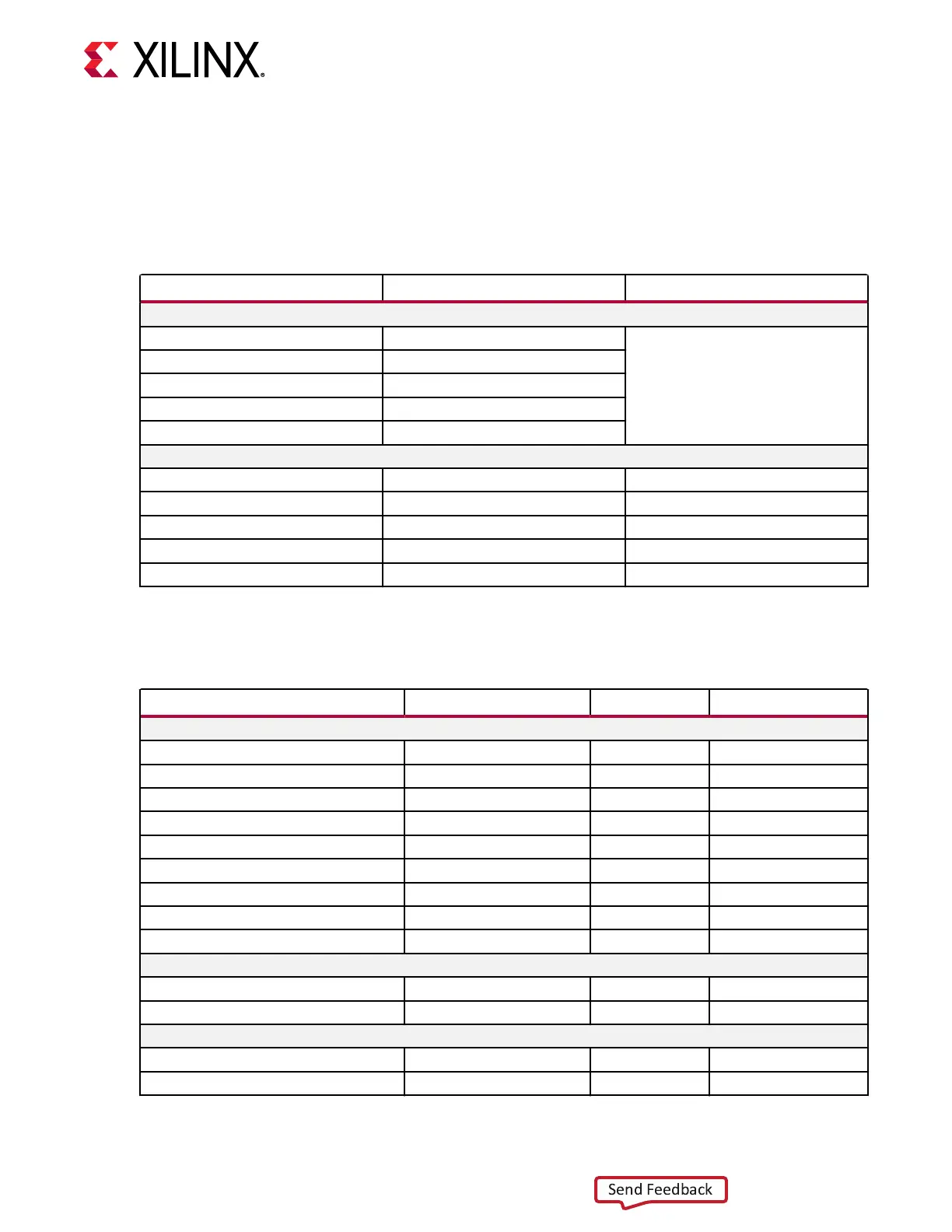

Table 17: ZCU208 Board Clock Sources

Clock (Net) Name Frequency Clock Source

Fixed Frequency Clocks

PS_REF_CLK 33.33 MHz

U43 SI5341B Clock Generator (0x76)

CLK_100 100 MHz

CLK_125 125 MHz

GTR_REF_CLK_SATA 125 MHz

GTR_REF_CLK_USB3 26 MHz

Programmable Frequency Clocks

USER_SI570_C0 300 MHz (Default) U47 SI570 I2C PROG. OSC. (0x5D)

USER_SI570_C1 300 MHz (Default) U130 SI570 I2C PROG. OSC. (0x5D)

USER_MGT_SI570_CLOCK 156.25 MHz (Default) U48 SI570 I2C PROG. OSC. (0x5D)

USER_SMA_MGT_CLOCK User-Provided Source J6 (P)/J7 (N) SMA CONN.

Various 8A34001 eCPRI Clocks Various U409 8A34001 (0x58)

The following table lists the connecons for each clock.

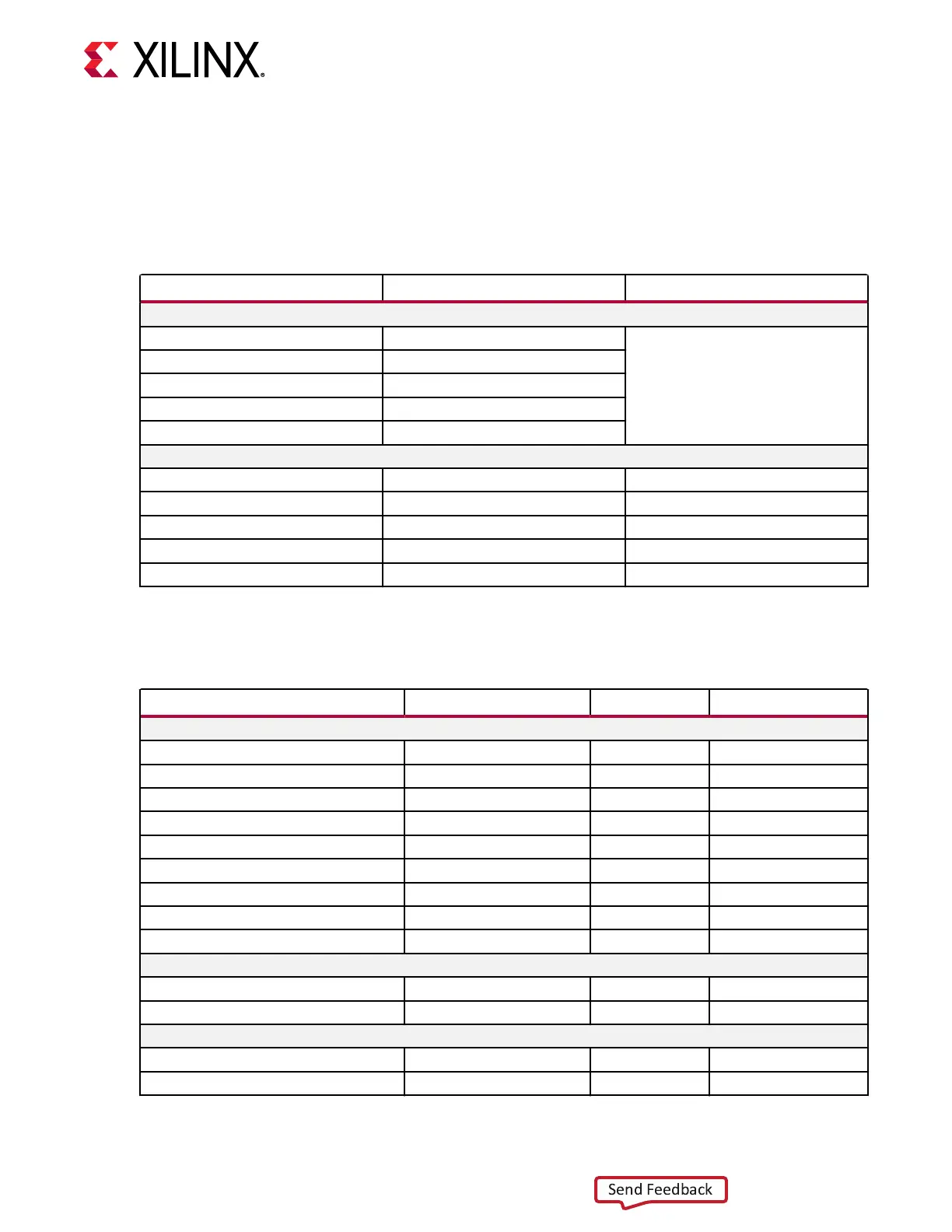

Table 18: Clock Connections to ZU48DR U1

Clock Source Ref. Des. and Pin Net Name I/O Standard ZU48DR (U1) Pin

U43 SI5341B Clock Generator

U43.59 PS_REF_CLK (series R300) 1 U32

U43.45 CLK_125_P LVDS A13

U43.44 CLK_125_N LVDS A12

U43.42 CLK_100_P LVDS G12

U43.41 CLK_100_N LVDS G11

U43.35 GTR_REF_CLK_SATA_P 2 AB34

U43.34 GTR_REF_CLK_SATA_N 2 AB35

U43.31 GTR_REF_CLK_USB3_P 2 AC36

U43.30 GTR_REF_CLK_USB3_N 2 AC37

U47 SI570 I2C Prog. Oscillator DDR4 C0 I/F (300 MHz default)

U47.4 USER_SI570_C0_P LVDS AR20

U47.5 USER_SI570_C0_N LVDS AR19

U130 SI570 I2C Prog. Oscillator DDR4 C1 I/F (300 MHz default)

U130.4 USER_SI570_C1_P LVDS G17

U130.5 USER_SI570_C1_N LVDS F17

Chapter 3: Board Component Descriptions

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 43

Loading...

Loading...