Logic

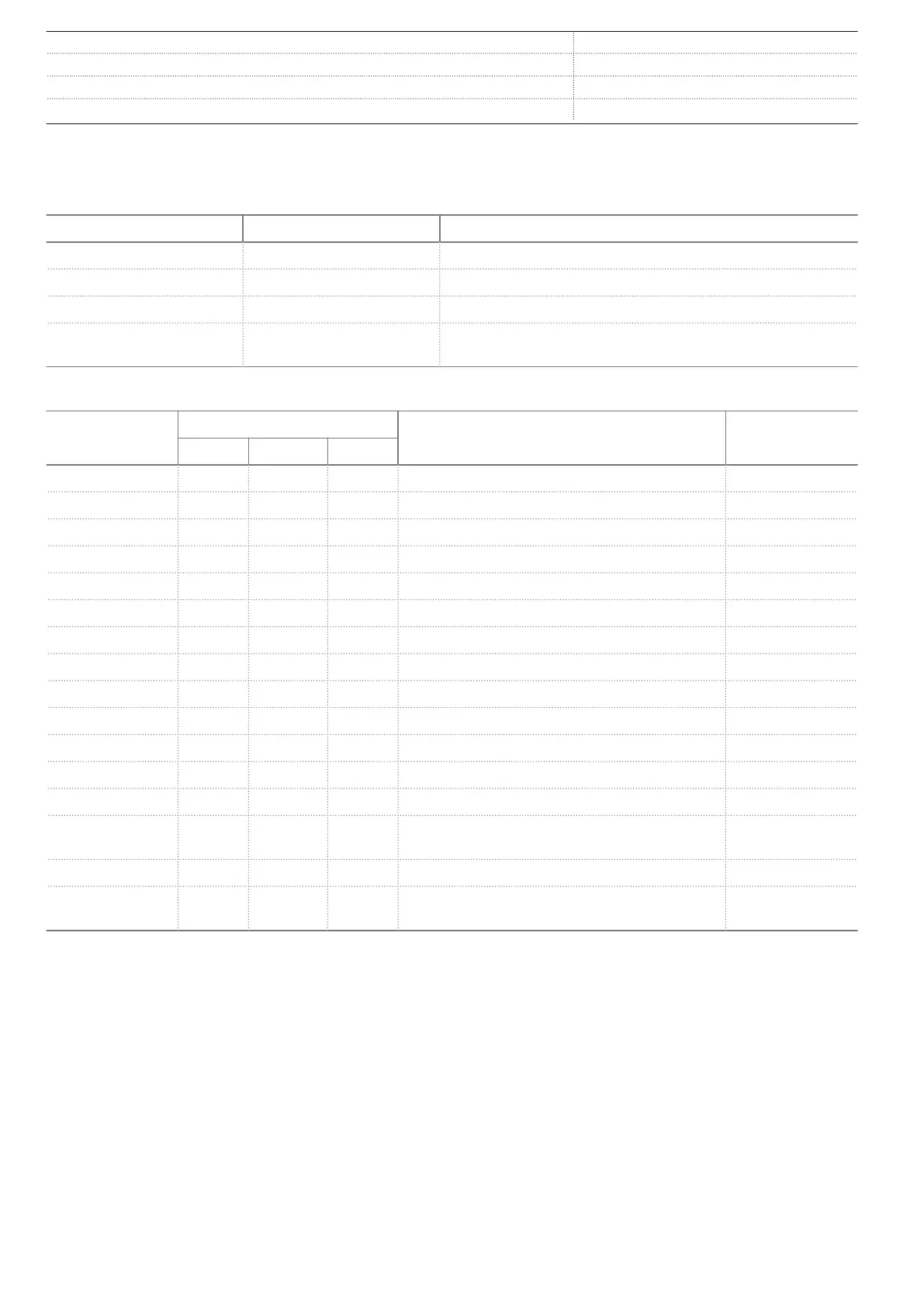

Table 75. Tripping logic common 3-phase output SMPPTRC

Function Range or value Accuracy

Trip action 3-ph, 1/3-ph, 1/2/3-ph -

Minimum trip pulse length (0.000-60.000) s ± 0.2% or ± 30 ms whichever is greater

3-pole trip delay (0.020-0.500) s ± 0.2% or ±10 ms whichever is greater

Single phase delay, two phase

delay and evolving fault delay

(0.000-60.000) s ± 0.2% or ±10 ms whichever is greater

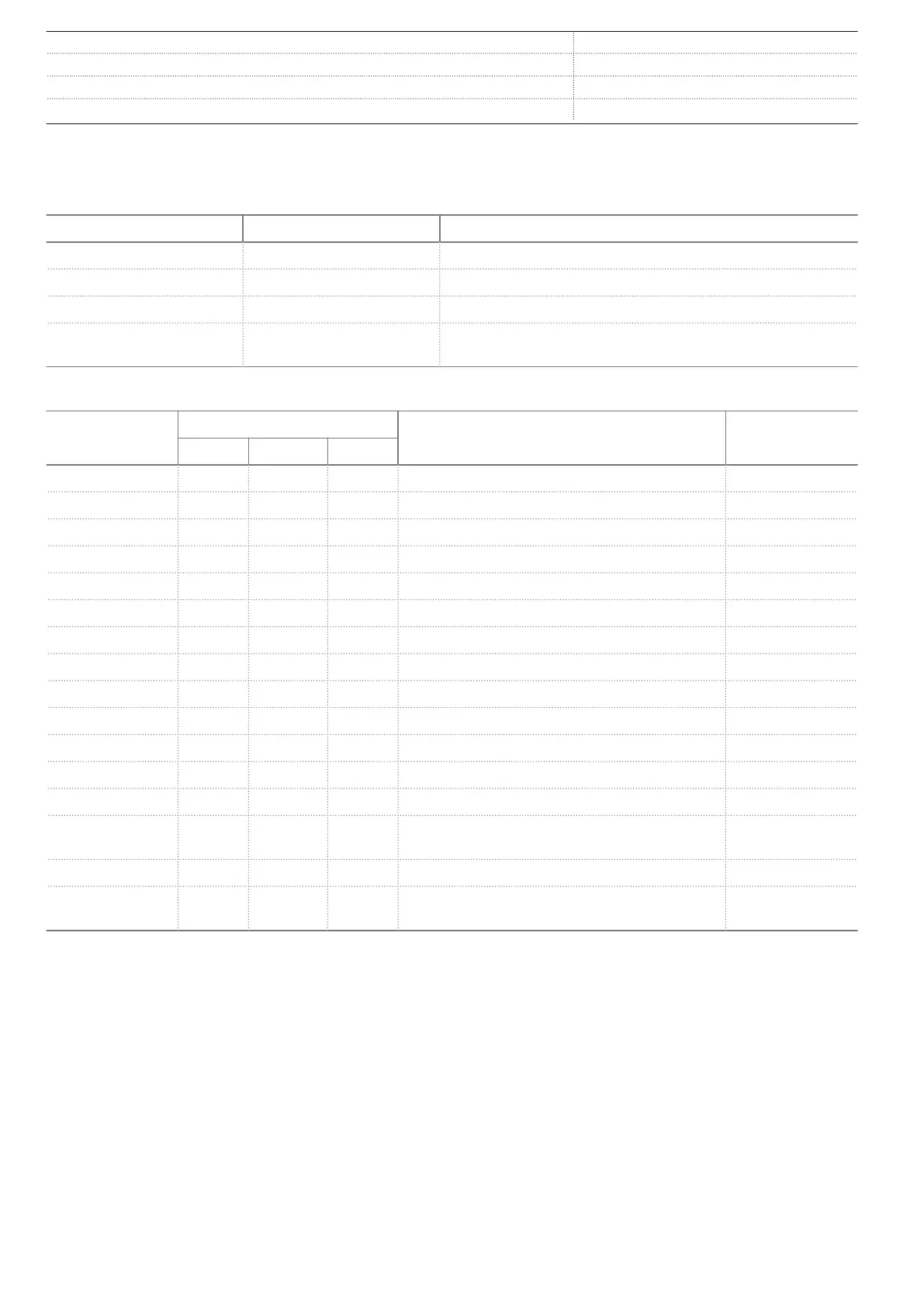

Table 76. Configurable logic blocks

Logic block

Quantity with cycle time Range or value Accuracy

fast medium normal

LogicAND 60 60 160 - -

LogicOR 60 60 160 - -

LogicXOR 10 10 20 - -

LogicInverter 30 30 80 - -

LogicSRMemory 10 10 20 - -

LogicRSMemory 10 10 20 - -

LogicGate 10 10 20 - -

LogicTimer 10 10 20 (0.000–90000.000) s ± 0.5% ± 10 ms

LogicPulseTimer 10 10 20 (0.000–90000.000) s ± 0.5% ± 10 ms

LogicTimerSet 10 10 20 (0.000–90000.000) s ± 0.5% ± 10 ms

LogicLoopDelay 10 10 20 (0.000–90000.000) s ± 0.5% ± 10 ms

Trip Matrix Logic 6 6 - - -

Boolean 16 to Integer 4 4 8 - -

Boolean 16 to integer

with Logic Node

4 4 8 - -

Integer to Boolean 16 4 4 8 - -

Integer to Boolean 16

with Logic Node

4 4 8 - -

Transformer protection RET670 2.0

1MRK 504 141-BEN C

Product version: 2.0

86 ABB

Loading...

Loading...