Altera Corporation 13

Nios Development Board Reference Manual, Cyclone Edition Board Components

The Cyclone

EP1C20 Device

U60 is a Cyclone EP1C20F400C7 device in a 400-pin FineLine BGA

®

package. Table 4 lists the Cyclone device features.

The development board provides two separate methods for configuring

the Cyclone device:

1. Using the Quartus II software running on a host computer, a

designer configures the device directly via an Altera download cable

connected to the Cyclone JTAG header (J24).

2. When power is applied to the board, a configuration controller

device (U3) attempts to configure the Cyclone device with hardware

configuration data stored in flash memory. For more information on

the configuration controller, see “Configuration Controller Device

(EPM7128AE)” on page 28.

f

See the Altera Cyclone literature page for Cyclone-related documentation

at www.altera.com/literature/lit-cyc.html including a Cyclone EP1C20

pinout document.

Flash Memory

Device

U5 is an 8 Mbyte AMD AM29LV065D flash memory device connected to

the Cyclone device and can be used for two purposes:

1. A Nios embedded processor implemented on the Cyclone device can

use the flash memory as general-purpose readable memory and non-

volatile storage.

2. The flash memory can hold Cyclone configuration data that is used

by the configuration controller to load the Cyclone device at power-

up. See “Configuration Controller Device (EPM7128AE)” on

page 28. for related information.

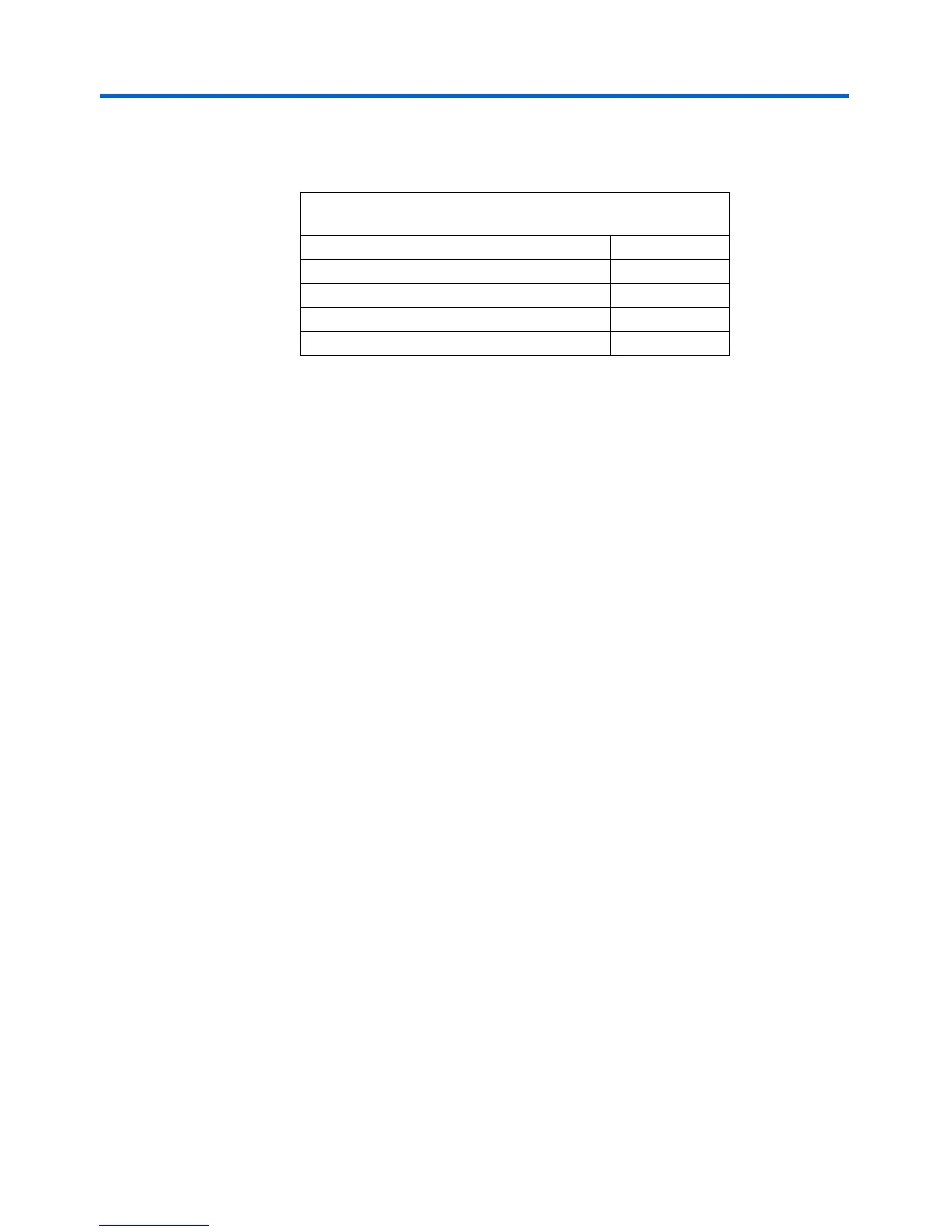

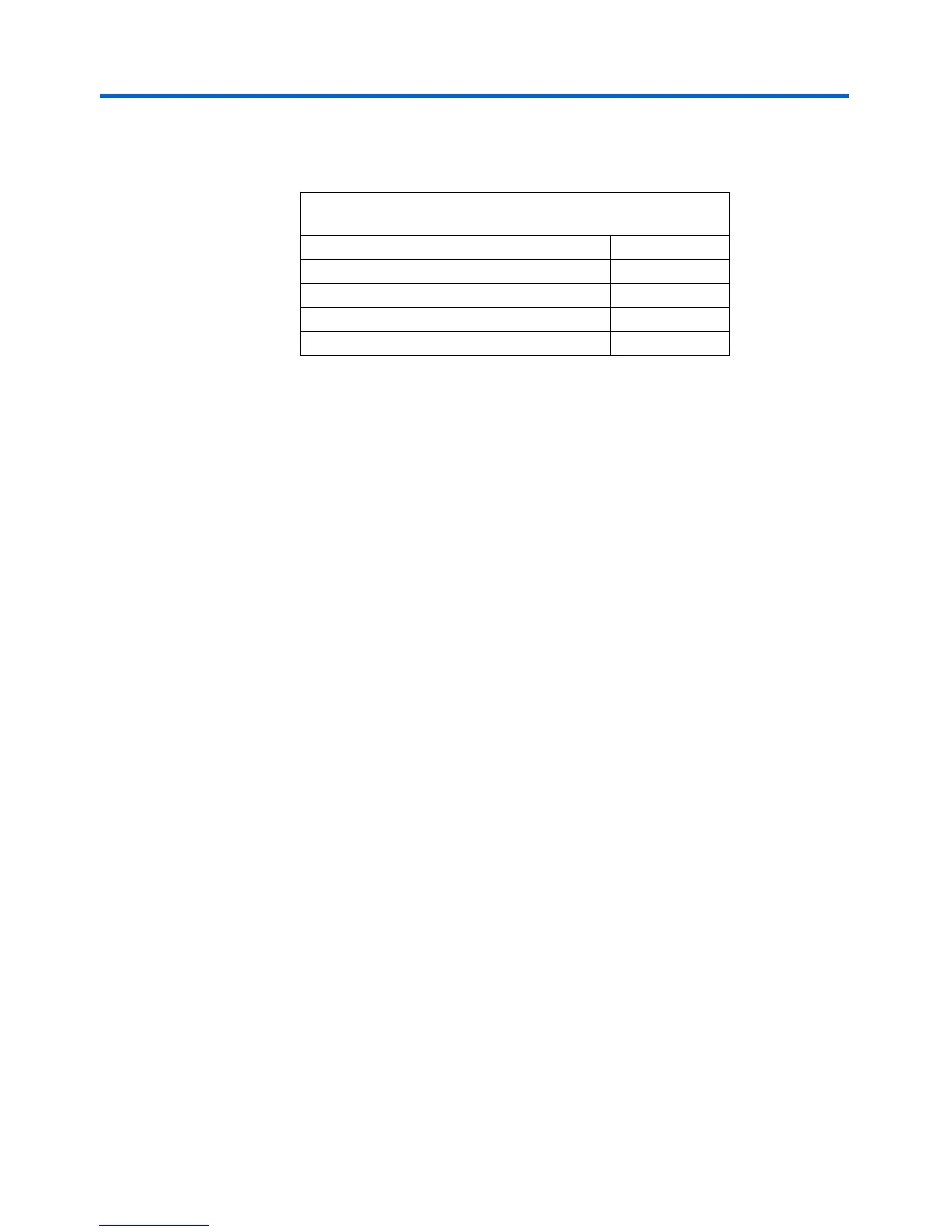

Table 4. Cyclone EP1C20 Device Features

Logic Elements 20,060

M4K RAM blocks (128 X 36 bits) 64

Total RAM bits 294,912

PLLs 2

Maximum user I/O pins 301

Loading...

Loading...