18 Altera Corporation

Board Components Nios Development Board Reference Manual, Cyclone Edition

f

See www.micron.com for detailed SDRAM information.

Dual SRAM

Devices

U35 and U36 are two (512 Kbyte x 16-bit) asynchronous SRAM devices.

They are connected to the Cyclone device so they can be used by a Nios

embedded processor as general-purpose memory. The two 16-bit devices

can be used in parallel to implement a 32-bit wide memory subsystem.

The pre-loaded Nios reference design identifies these SRAM devices in its

address space as a contiguous 1Mbyte, 32-bit-wide, zero-wait-state main

memory.

The SRAM devices share address and data connections with the flash

memory and the Ethernet MAC/PHY device. For shared bus information,

see “Appendix A: Shared Bus Table” on page 39.

f

See www.idt.com for detailed information about the SRAM devices.

Ethernet

MAC/PHY

The LAN91C111 (U4) is a mixed signal analog/digital device that

implements protocols at 10Mbps and 100 Mbps. The control pins of U4 are

connected to the Cyclone device so that Nios systems can access Ethernet

via the RJ-45 connector (RJ1). See Figure 4 on page 19. The Nios

development kit includes hardware and software components that allow

Nios processor systems to communicate with the LAN91C111 Ethernet

device.

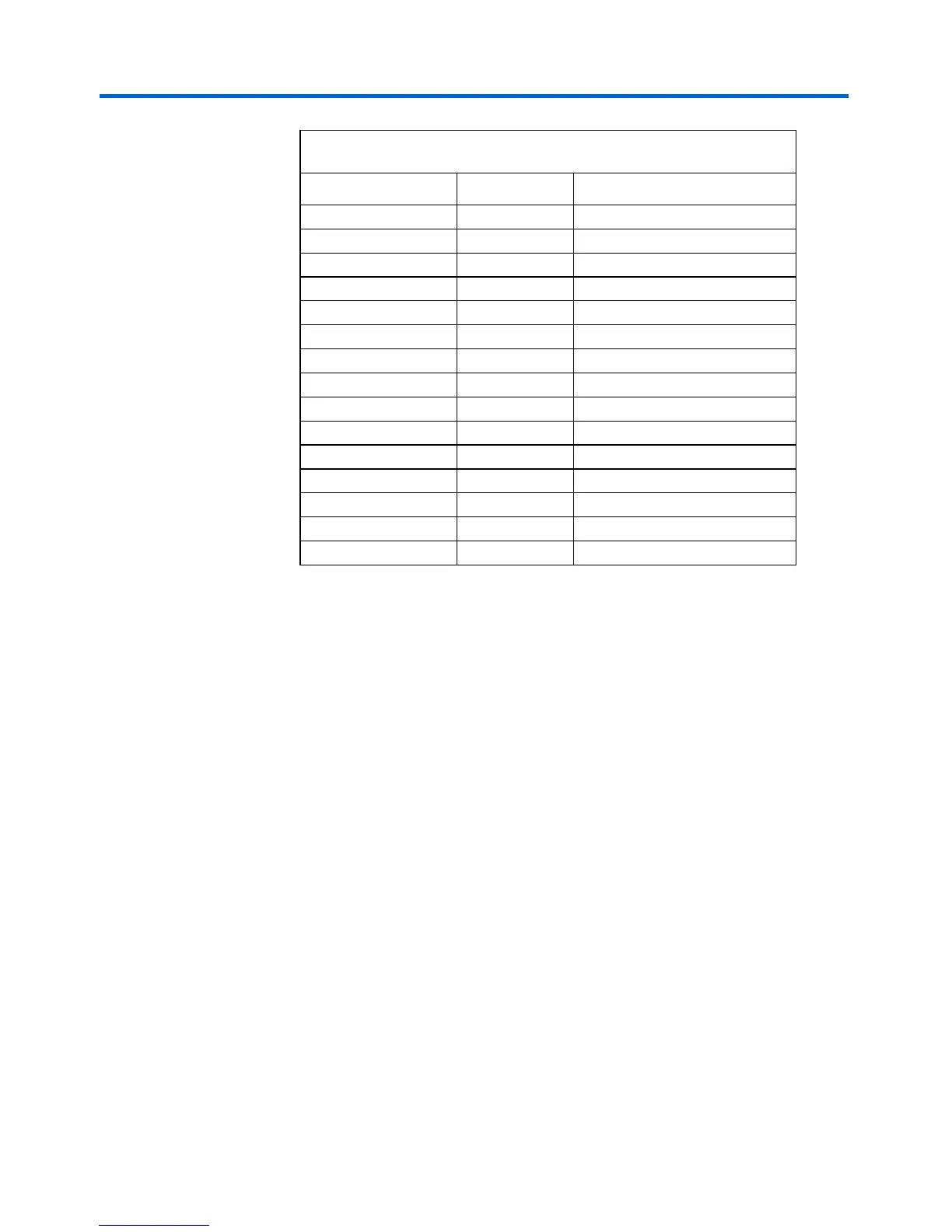

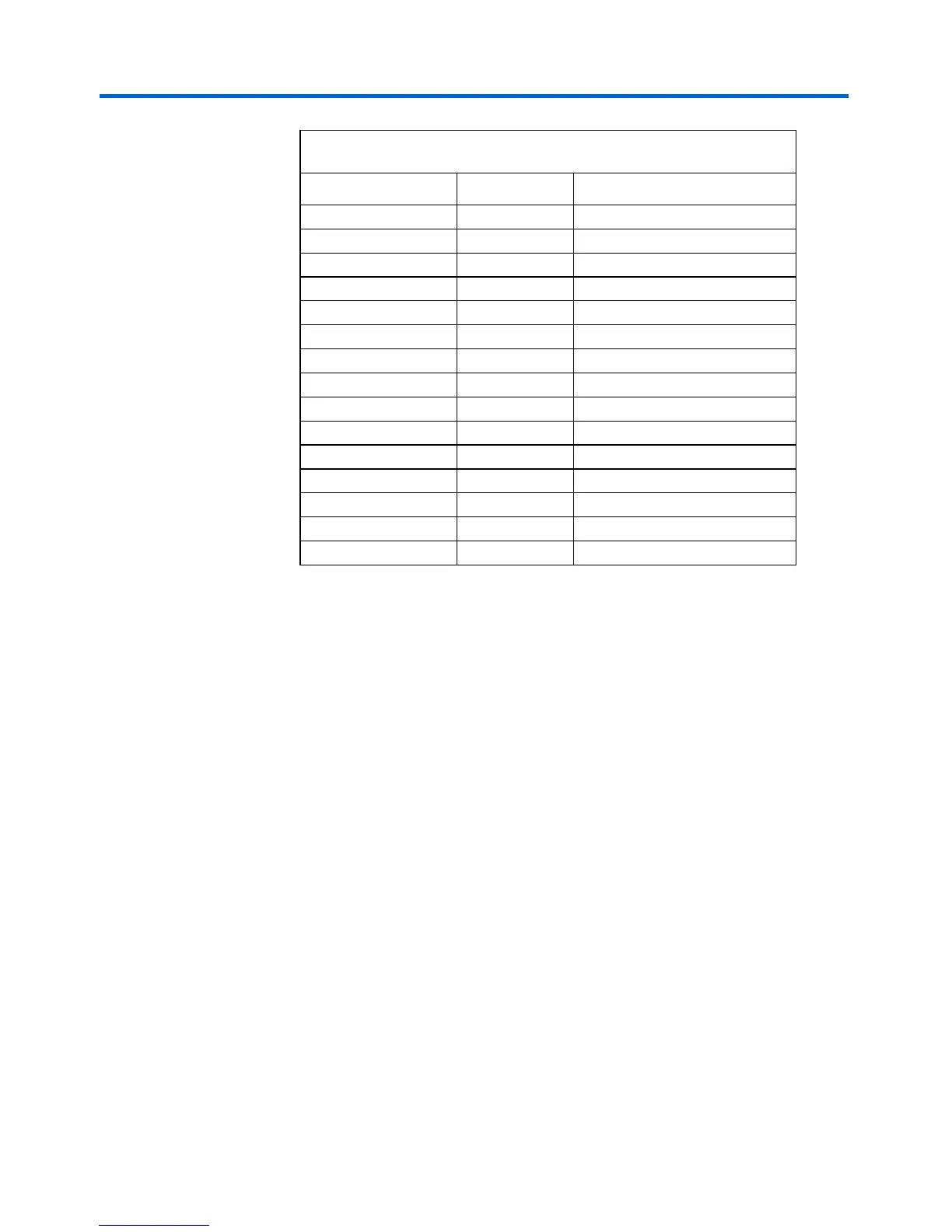

DQ27 50 U4

DQ28 51 U2

DQ29 53 U3

DQ30 54 V3

DQ31 56 V2

DQM0 16 J2

DQM1 71 J1

DQM2 28 H4

DQM3 59 H3

RAS_N 19 H2

CAS_N 18 G3

CKE 67 G7

CS_N 20 G6

WE_N 17 G4

CLK 68 L13

Table 6. SDRAM (U57) Pin Table (Part 3 of 3)

Pin Name Pin Number Connects to Cyclone Pin

Loading...

Loading...