0.6 (2019–07–25)

Amlogic Proprietary and Confidential

Copyright © Amlogic. All rights reserved.

45

Symbol Description Min. Typ. Max. Unit Notes

C

L

Load

Capacitance

7.5 12 12.5 pF

ESR Equivalent

Series

Resistance

100 oHm

Note

1. 10ppm Tolerance is preferred if 24MHz XTAL is also driving WIFI module.

2. For user external clock source, Please connect input clock output to SYS_OSCIN , let

SYS_OSCOUT floating.

3. The threshold of Xin inverter is around 0.9V (Xin range: -0.3V to +2.1V). Therefore,

Following suggestion for input clock.

●● Suggestion 1: Without DC blocking capacitor, use a higher Vpp output TCXO. The high

voltage should be higher than 1.35V (VSWING >1.35V, 0V to >1.35V).

●● Suggestion 2: With DC blocking capacitor, re-bias the middle voltage at 0.9V, VSWING

>2*0.45V;

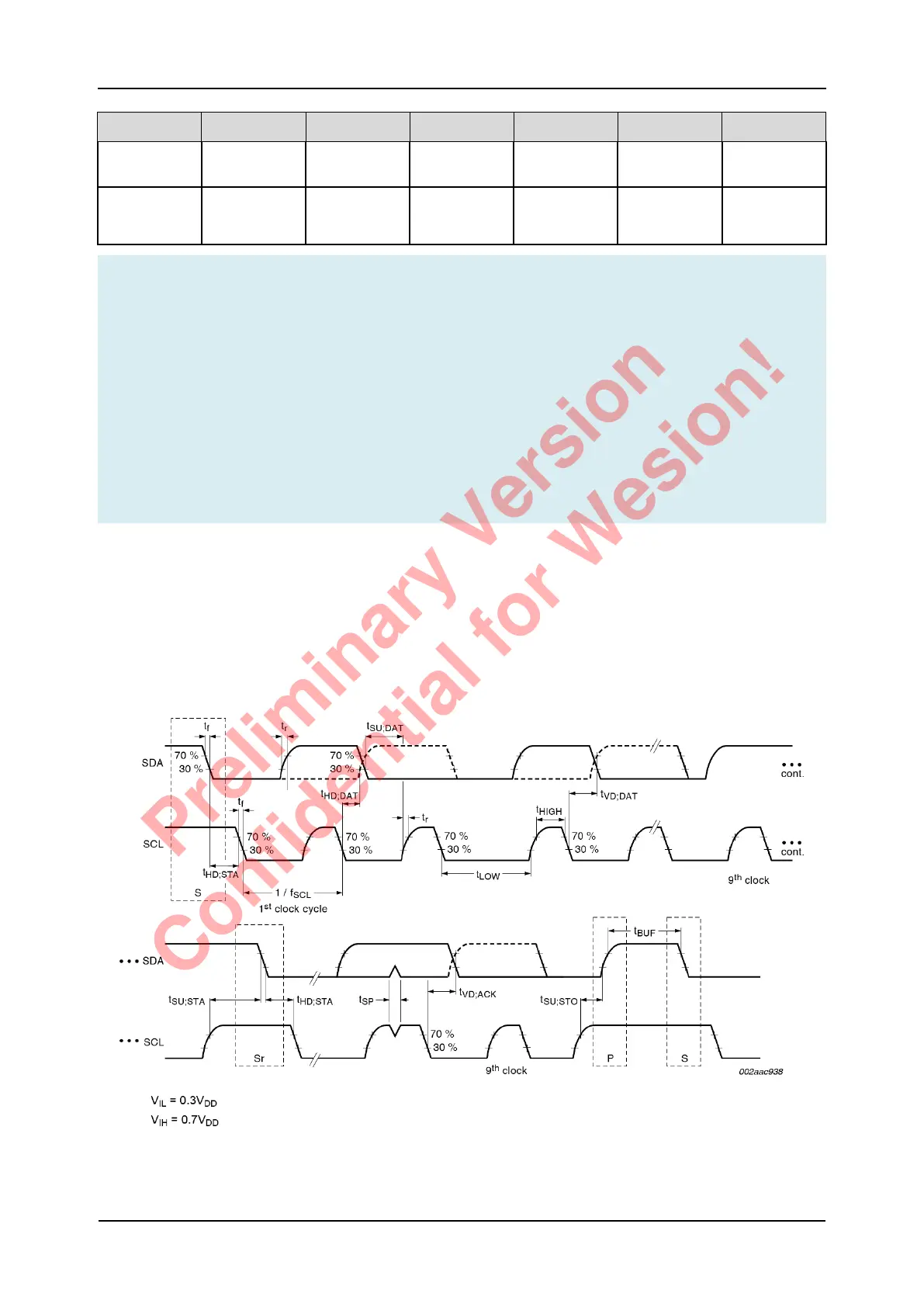

5.7 Timing Information

5.7.1 I2C Timing Specification

The I2C master interface Fast/Standard mode timing specifications are shown below.

Figure 5-1 I2C Interface Timing Diagram, FS mode

S905D3 Quick Reference Manual 5 Operating Conditions

Preliminary Version

Confidential for Wesion!

Loading...

Loading...