0.6 (2019–07–25)

Amlogic Proprietary and Confidential

Copyright © Amlogic. All rights reserved.

46

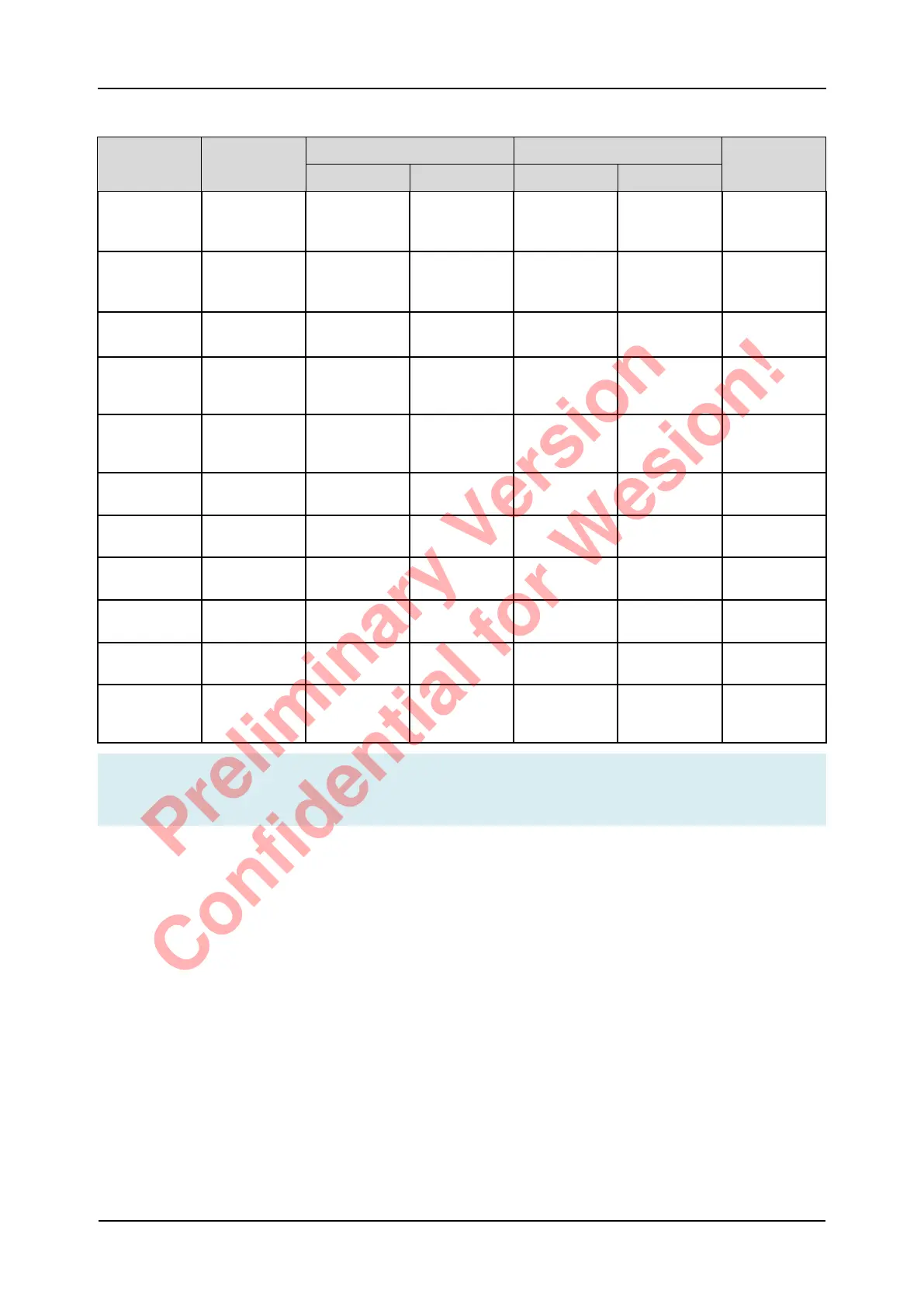

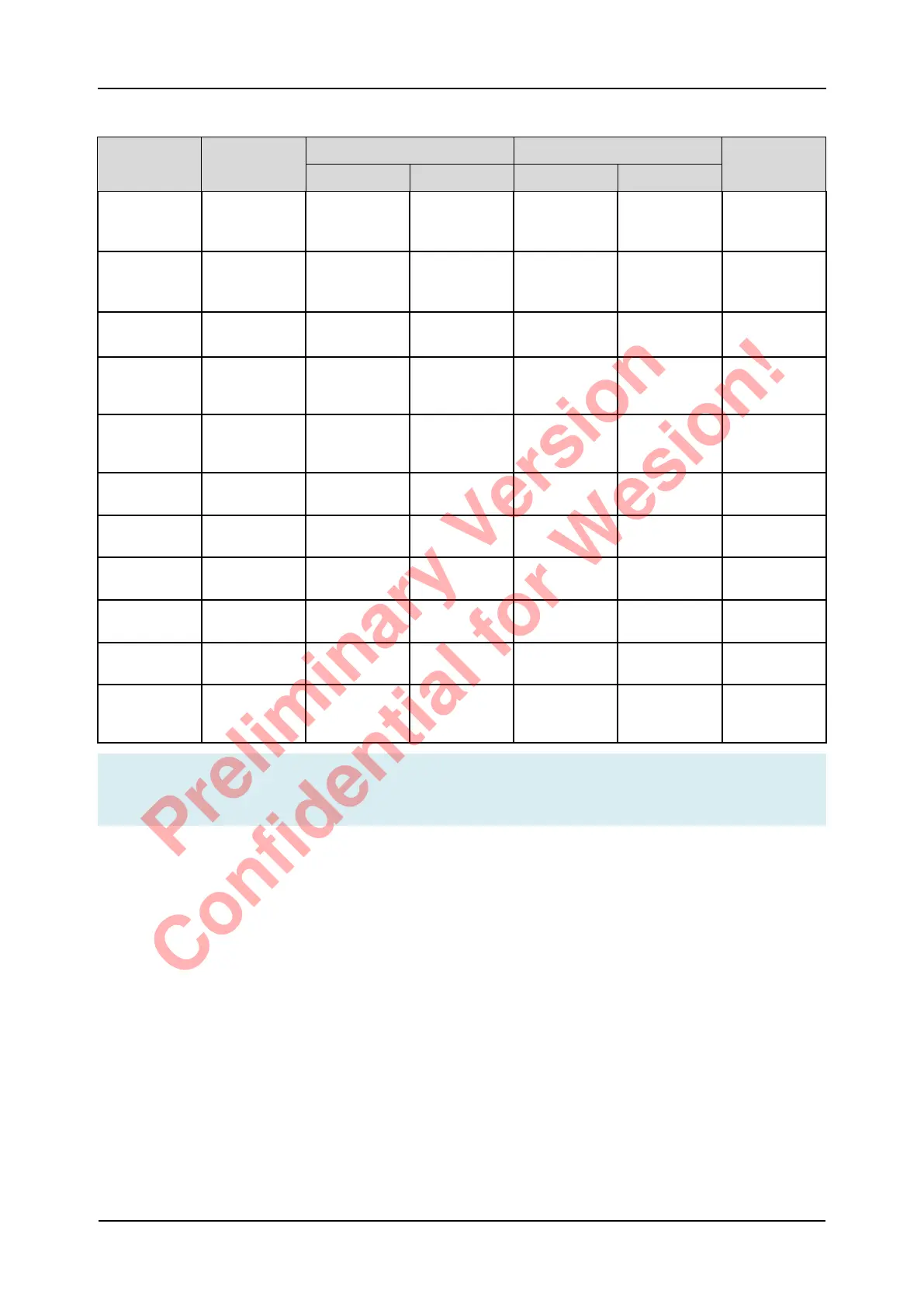

Table 5-1 I2C Interface Timing Specification, SF mode

Symbol Parameter Standard-mode Fast-mode Unit

Min. Max Min Max

tR Rise time of

SDA and SCL

signals

- 1000 - 300 ns

tF Fall time of

SDA and SCL

signals

- 300 - 300 ns

fSCL SCL clock

frequency

- 100 - 400 KHz

tLOW LOW period

of the SCL

clock

4.7 - 1.3 - µs

tHIGH HIGH period

of the SCL

clock

4 - 0.6 - µs

tSu;STA Setup time for

START

4.7 - 0.6 - µs

tSu;DAT Setup time for

SDA

250 - 100 - ns

tSu;STO Setup time for

STOP

4 - 0.6 - µs

tHd;STA Hold time for

START

4 - 0.6 - µs

tHd;DAT Hold time for

SDA

0 3.45 0 0.9 µs

tBuf Bus free time

between stop

and start

4.7 - 1.3 - µs

Note

●● Open drain does not support driver strength adjustment.

5.7.2 EMMC/SD Timing Specification

Timing specification for EMMC and SDIO are shown as below.

S905D3 Quick Reference Manual 5 Operating Conditions

Preliminary Version

Confidential for Wesion!

Loading...

Loading...