0.6 (2019–07–25)

Amlogic Proprietary and Confidential

Copyright © Amlogic. All rights reserved.

3

3 Features Summary

CPU Sub-system

●● Quad core ARM Cortex-A55 CPU

●● ARMv8-A architecture with Neon and Crypto extensions

●● 8-stage in-order full dual issue pipeline

●● Unified system L3 cache

●● Build-in Cortex-M4

Optional

core for always on processing

●● Build-in Cortex-M3 core for system control processing

●● Advanced TrustZone security system

●● Application based traffic optimization using internal QoS-based switching fabrics

Neural Network Processing Unit(NPU)

Optional

●● 1.2 TOPS NN inference accelerator

●● Supports all major deep learning frameworks including TensorFlow and Caffe

3D Graphics Processing Unit

●● ARM G31 MP2 GPU

●● 4-wide warps, dual texture pipe, 2x 4-wide execution engines (EE)

●● Concurrent multi-core processing

●● OpenGL ES 3.2, Vulkan 1.1 and OpenCL 2.0 support

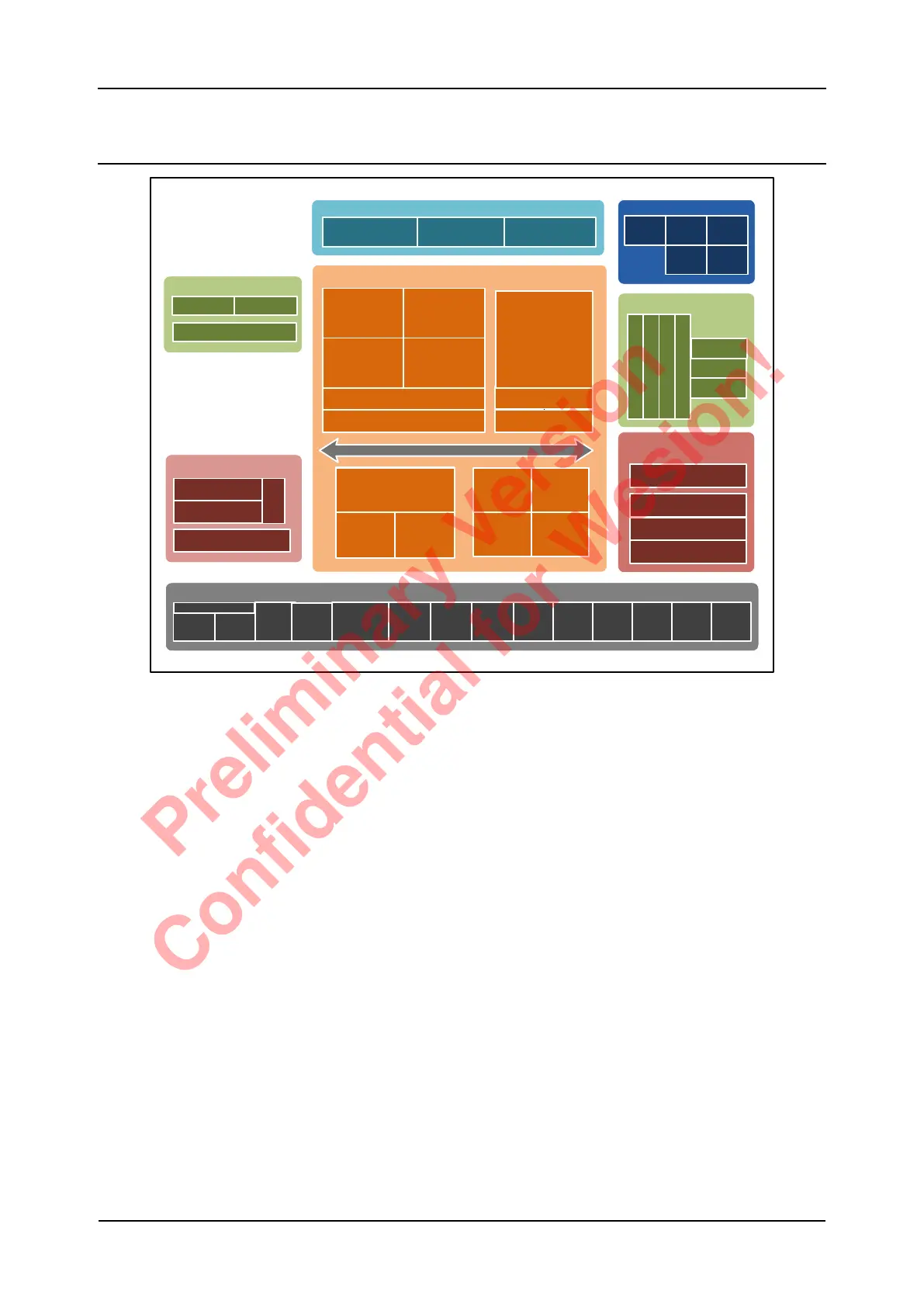

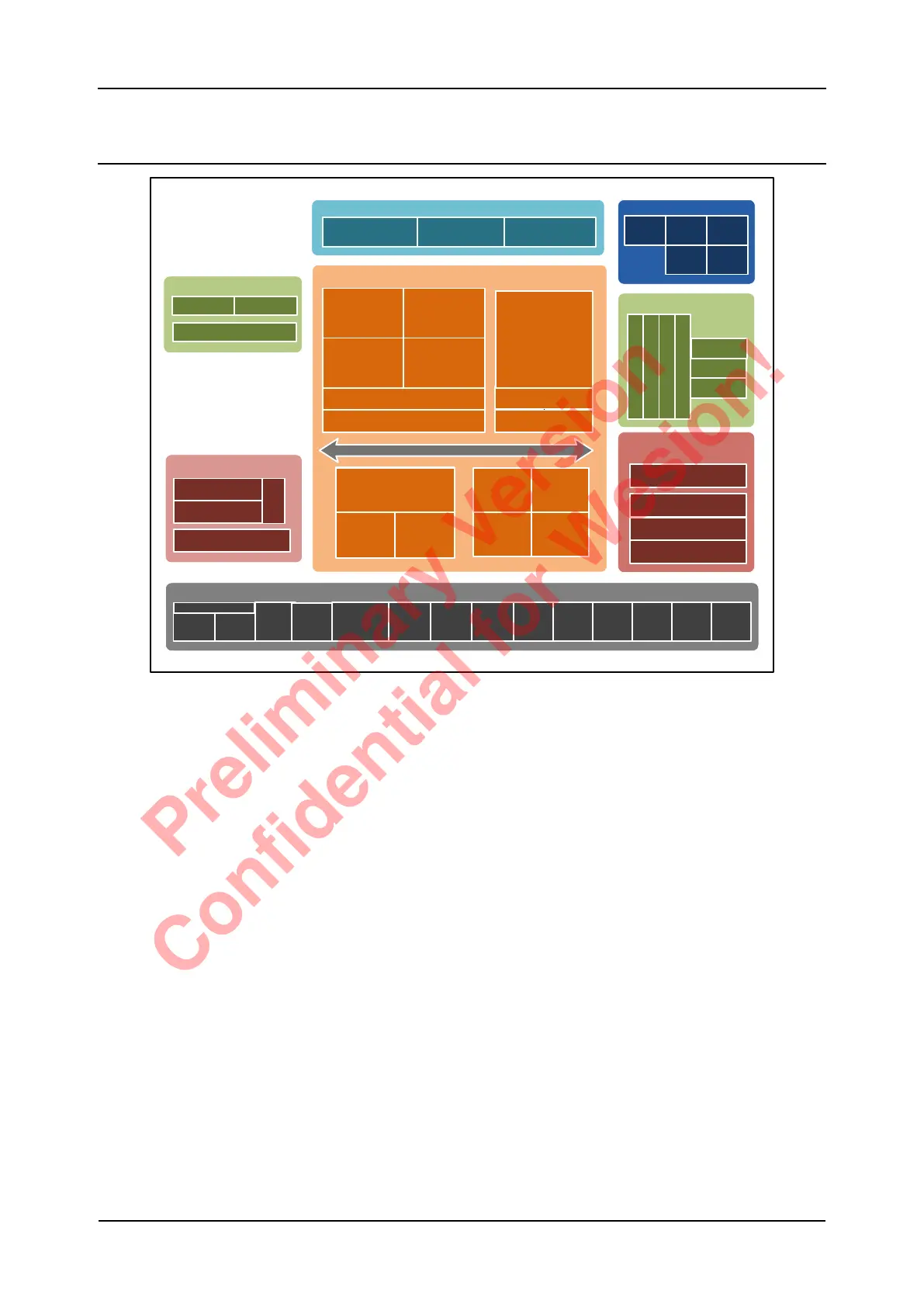

S905D3

Memory InterfaceSystem Interface

Video Output Unit

De-interlacer

Scalar

HDRProcessing

HDMI 2.1

Core and Fabric

TrustZone Security

Input/Output Interfaces

USB

HOST

USB

OTG

SDIO3.0I2CUARTSPIPWM

SAR

ADC

SDXC/

SDHC/

SD

L3Cache

MMU

Audio Output Unit

TDM / I2S

HDMI 2.1

SPDIF

IR

Rx & Tx

PLLsPMUJTAG

Temp

Sensor

PerfMon

Audio Input Unit

SPDIF

DDR3/4/3L &

LPDDR3/4 Memory

Controller

eMMC/NAND Flash

Controller

SPI

Flash Controller

2.5D Graphic

Processing

Crypto

Engine

Secured NV

storage

Power

Management

Processor

10/100M

Ethernet

PHY

CVBS

TDM / I2S

Cortex-A55

32KB I/D-Cache

NEON/VFP

Cortex-A55

32KB I/D-Cache

NEON/VFP

Cortex-A55

32KB I/D-Cache

NEON/VFP

Cortex-A55

32KB I/D-Cache

NEON/VFP

PDM x8

Stereo Audio DAC

Enhancement

L2 Cache

MMU

Mali-G31 MP2

Video Input Unit

2x TsinDemux

MIPI-CSI

MIPI DSI

Giga

Ethernet

MAC

USB SS/

PCIe 2.0

USB 3.0 / PCIe 2.0 *

ISO7816

* Supported configuration: PCIe 2.0 port + USB 2.0 Host, or USB 3.0 port without PCIe

A06ST01

NPU

#

Cortex-M4

#

AVE-10

VAD

# Optional for special part no.

S905D3 Quick Reference Manual 3 Features Summary

Preliminary Version

Confidential for Wesion!

Loading...

Loading...