0.6 (2019–07–25)

Amlogic Proprietary and Confidential

Copyright © Amlogic. All rights reserved.

53

Symbol Parameter (-

Asynchronous) (-

mode 5)

Min Max Unit

tALH ALE hold 5 - ns

tDS Data setup time 7 - ns

tDH Data hold time 5 - ns

tWC WE# cycle time 20 - ns

tWP WE# pulse width 10 - ns

tWH WE# high lold time 7 - ns

tREA RE# access time - 16 ns

tOH Data output hold

time

15 - ns

tRLOH RE#-low to data hold

time (EDO)

5 - ns

tRP RE# pulse width 10 - ns

tREH RE# high hold time 7 - ns

tRC RE# cycle time 20 - ns

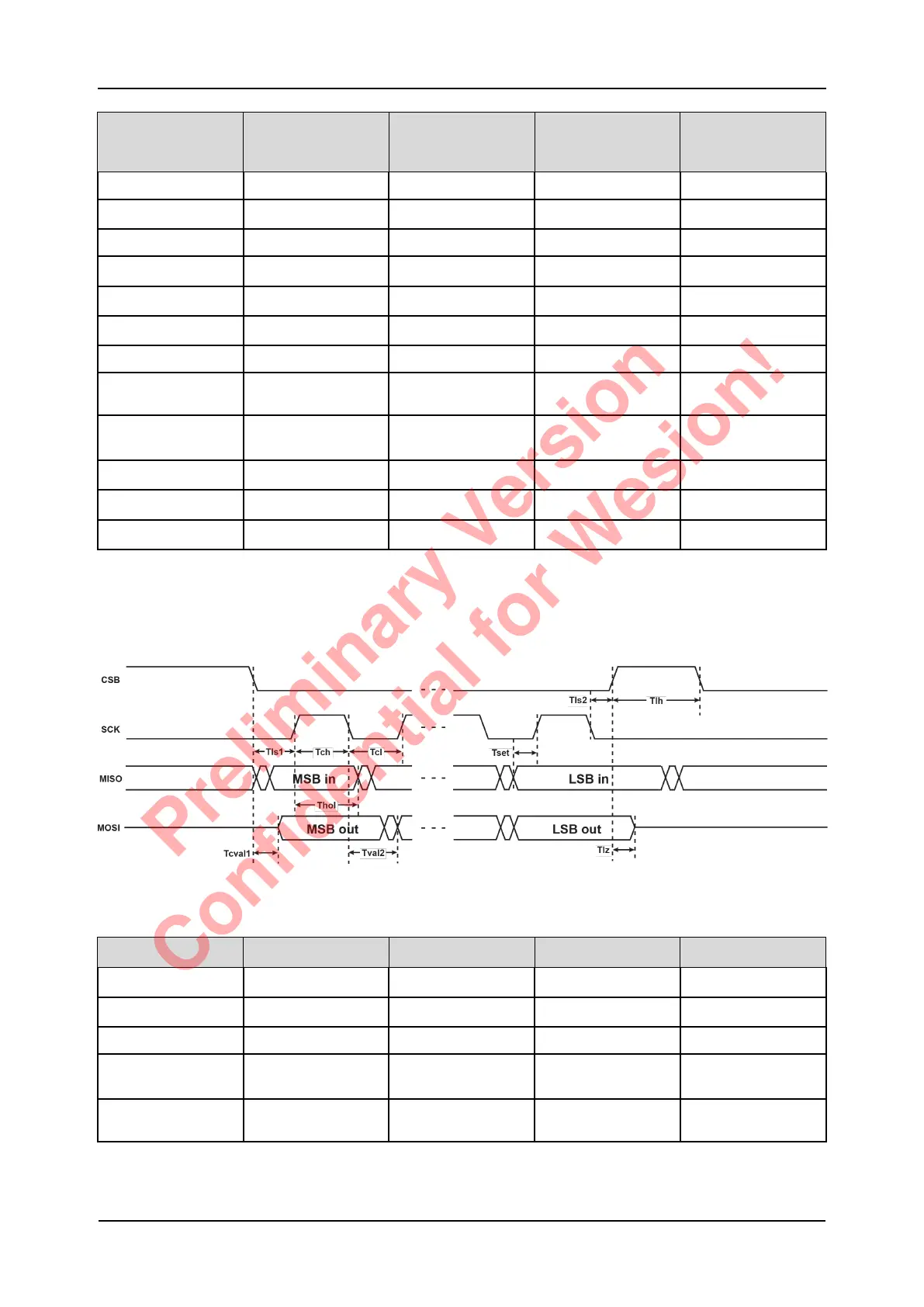

5.7.4 SPICC Timing Specification

Figure 5-11 SPICC Timing Diagram

Table 5-9 SPICC Master Timing Specification

Symbol Description Min. Max. Unit

fCLK Clock Frequency 1 80 MHz

TCH Clock high time 5 ns

TCL Clock low time 5 ns

TLS1 CS fall to First Rising

CLK Edge

50 ns

TSET Data input Setup

Time

4 ns

S905D3 Quick Reference Manual 5 Operating Conditions

Preliminary Version

Confidential for Wesion!

Loading...

Loading...