Axpert-Eazy AC Variable Frequency Drive

6-113

6

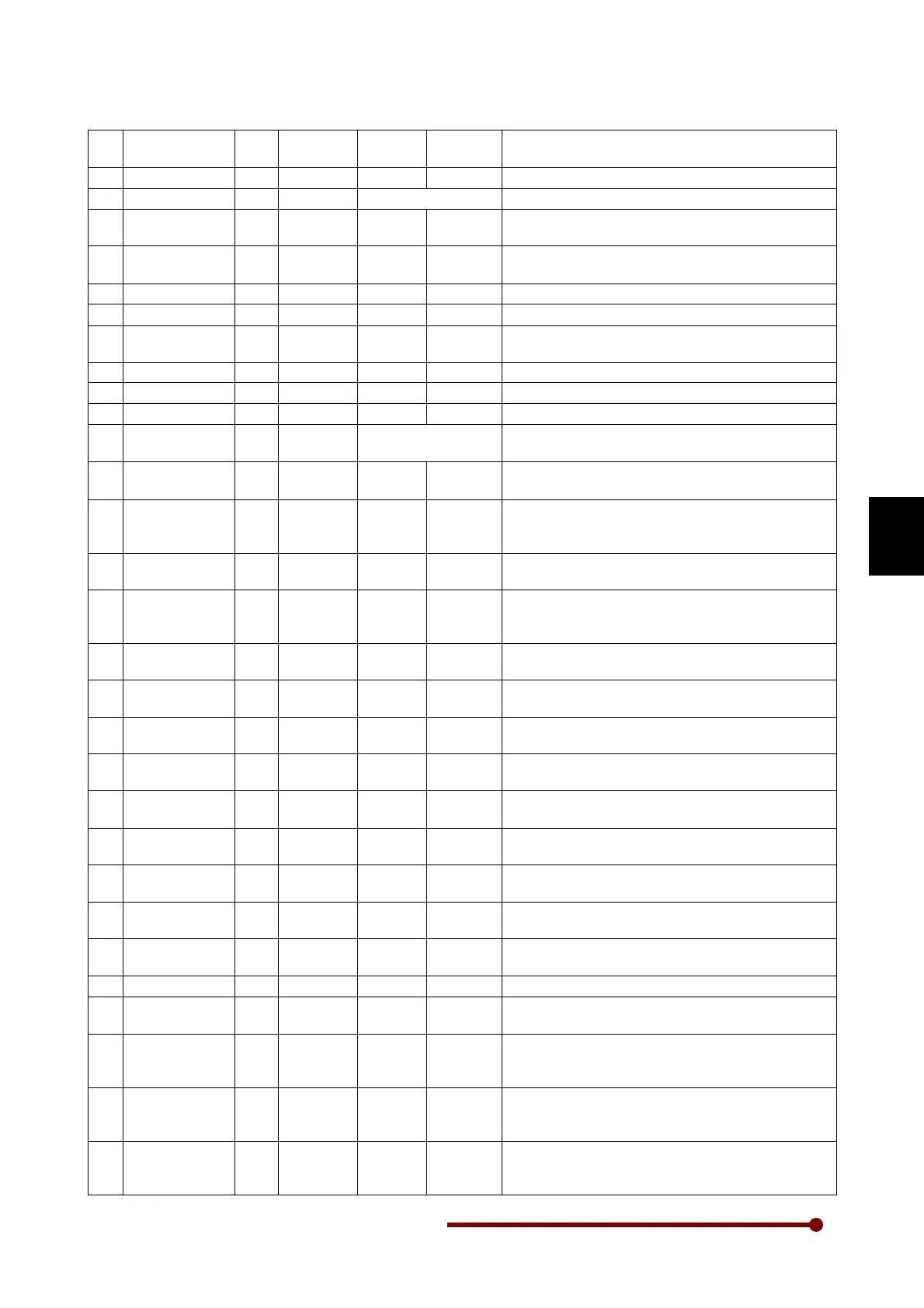

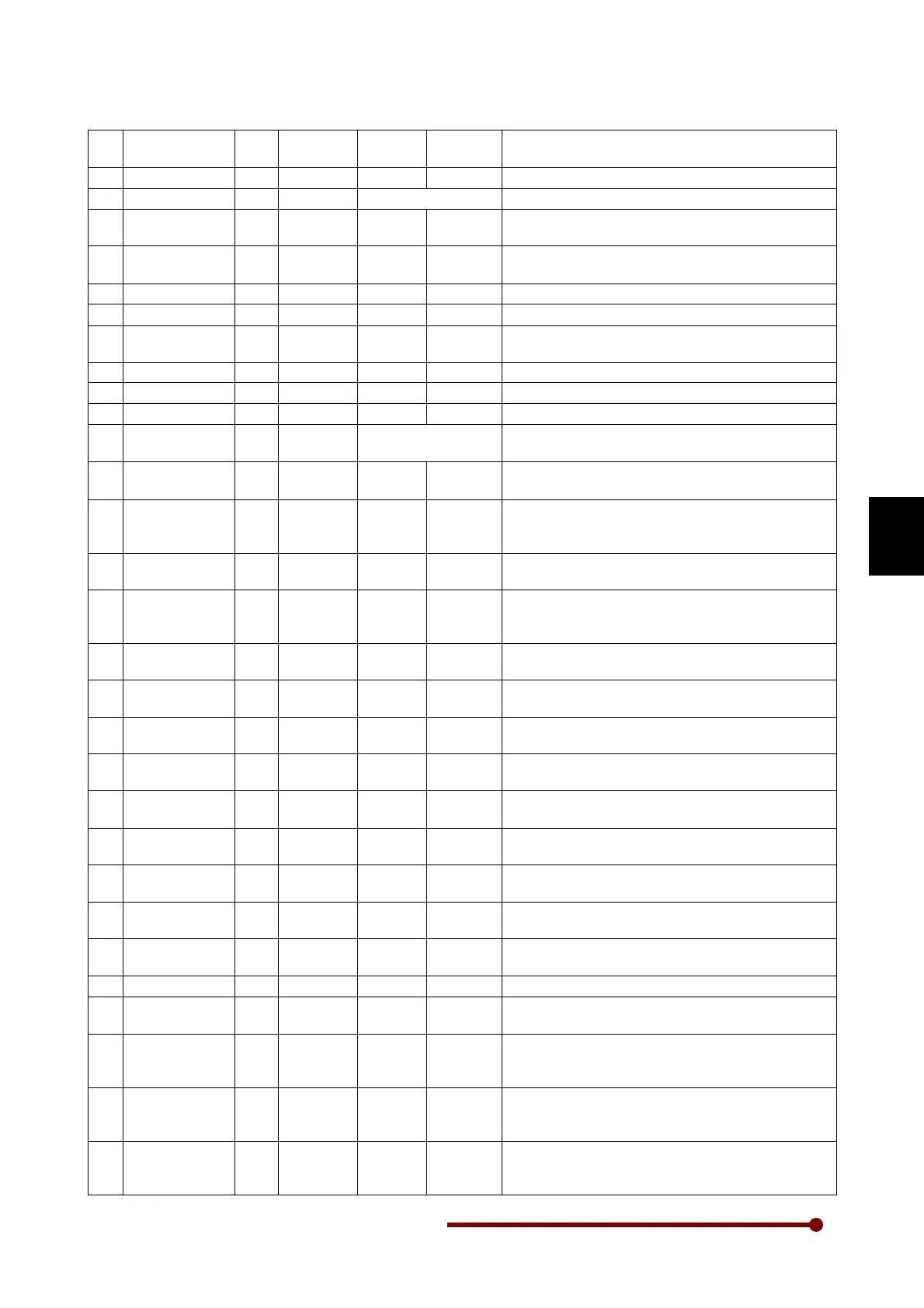

No.

Name

Code

1 END 000 000 000 000 End of the Program.

2 REG_LD 001 Register (n)

Value Load the 16-bit value in Register (n).

3 REG32_LD 002 Register (n)

000 000 Register (n) as a High 16-bit and Register (n+1) as a

Low 16-bit are loaded in Register 32 as 32 bits.

4 REG32_ST 003 Register (n)

000 000 Register 32 is store in Register (n) as a High 16-bit

and Register (n+1) as a Low 16-bit as 32 bit.

5 REGDEC 005 Register (n)

000 000 Decrement the value of Register (n) by 1.

6 REGINC 006 Register (n)

000 000 Increment the value of Register (n) by 1.

7 COPY_REG 007 Register (n)

Register

(m)

000 Copy Register (m) in Register (n).

8 COPY_FLG 008 Flag (n) Flag (m) 000 Copy Flag (m) in Flag (n).

9 SET_FLG 009 Flag (n) 000 000 Set the Flag (n).

10 CLEAR_FLG 010 Flag (n) 000 000 Clear the Flag (n).

11 ADI 011 Register (n)

Value Add immediate value. (Register (n) = Register (n) +

Immediate Value (0 to 32767)

12 ADD 012 Register (n)

Register

(n1)

Register

(n2)

Add operation. (Register (n) = Register (n1) +

Register (n2)).

13 ADD32 013 Register (n)

000 000 Register (n) as a High 16-bit and Register (n+1) as a

Low 16-bit are added to Register 32 as 32 bits.

Register 32 = Register 32 + Register (n).

14 SUB 014 Register (n)

Register

(n1)

Register

(n2)

Subtraction operator (Register (n) = Register (n1) -

Register (n2)).

15 SUB32 015 Register (n)

000 000 Register (n) as a High 16-bit and Register (n+1) as a

Low 16-bit are subtracted from Register32 as 32 bits.

Register 32 = Register 32 - Register (n).

16 MUL32 016 Register (n)

Register

(m)

000 Multiplication operator (Register 32 = Register (n) *

Register (m)).

17 DIV 017 Register (n)

Register

(n1)

Register

(n2)

Division operator (Register (n) = Register (n1) /

Register (n2)).

18 DIV32 018 Register (n)

000 000 Division operator (Register 32 = Register 32 /

Register (n)).

19 AND 019 Flag (n) Flag (n1)

Flag (n2) Logical AND operation between Flags (Flag (n) =

Flag (n1) & Flag (n2))

20 NAND 020 Flag (n) Flag (n1)

Flag (n2) Logical NAND operation between Flags (Flag (n) =

~(Flag (n1) & Flag (n2)))

21 NOR 021 Flag (n) Flag (n1)

Flag (n2) Logical NOR operation between Flags (Flag (n) = ~

(Flag (n1) | Flag (n2)).

22 XOR 022 Flag (n) Flag (n1)

Flag (n2) Logical XOR operation between Flags (Flag (n) =

Flag (n1) ^ Flag (n2)).

23 XNOR 023 Flag (n) Flag (n1)

Flag (n2) Logical XNOR operation between Flags (Flag (n) = ~

(Flag (n1) ^ Flag (n2))).

24 OR 024 Flag (n) Flag (n1)

Flag (n2) Logical OR operation between Flags (Flag (n) = Flag

(n1) | Flag (n2)).

25 NOT_FLG 025 Flag (n) Flag (m) 000 Invert the specified Flag (Flag (n) = ~Flag (m)).

26 NOT_REG 026 Register (n)

Register

(m)

000 Invert the specified register (Register (n) = ~Register

(m))

27 WAND 027 Register (n)

Register

(n1)

Register

(n2)

Logical Word (16-bit) AND operation between

registers (Register (n) = Register (n1) & Register

(n2))

28 WOR 028 Register (n)

Register

(n1)

Register

(n2)

Logical Word (16-bit) OR operation between

registers (Register (n) = Register (n1) | Register (n-

2))

29 WXOR 029 Register (n)

Register

(n1)

Register

(n2)

Logical Word (16-bit) XOR operation between

registers (Register (n) = Register (n1) ^ Register

(n2))

Loading...

Loading...