183

7598H–AVR–07/09

ATtiny25/45/85

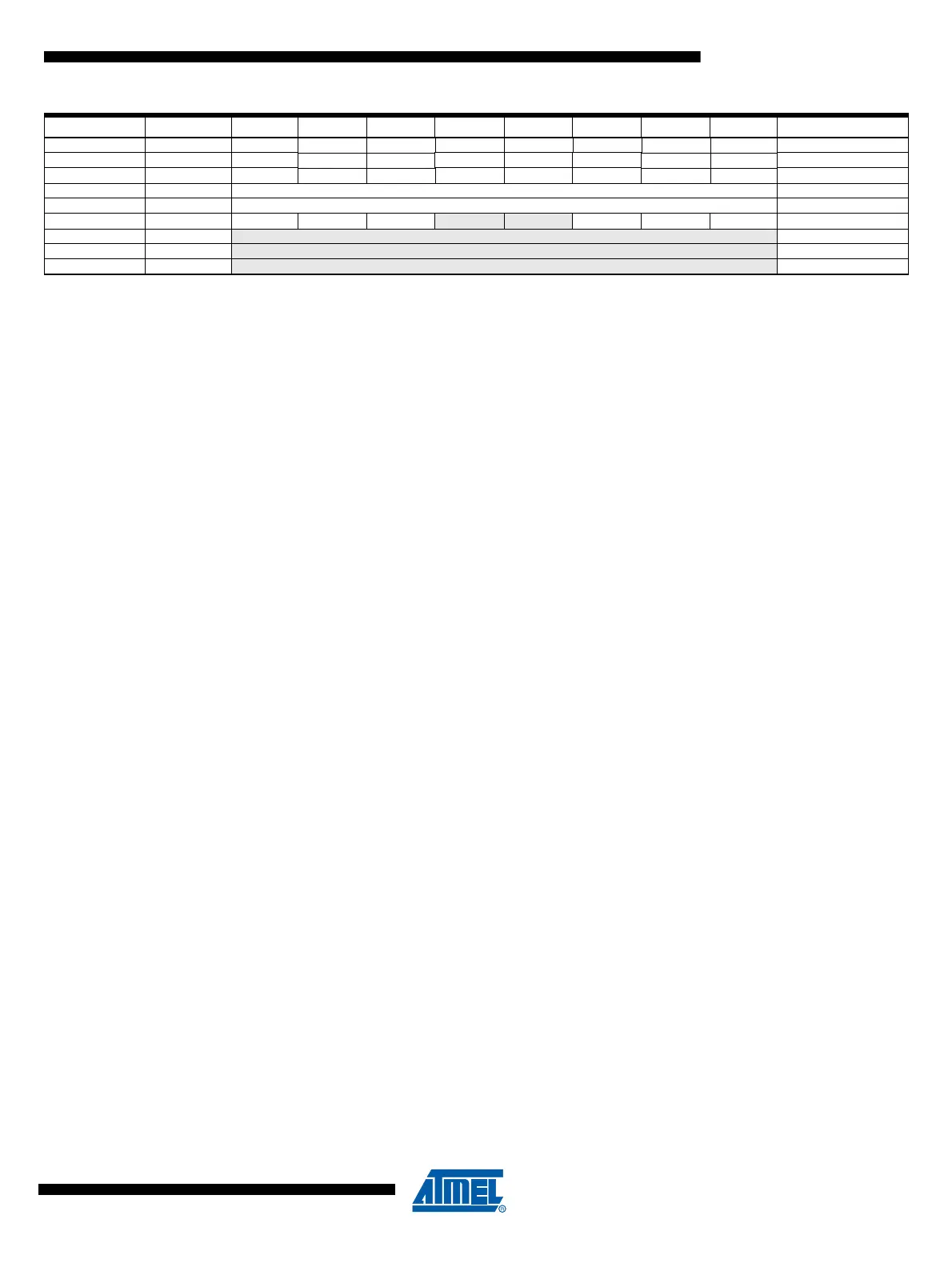

0x08 ACSR ACD ACBG ACO ACI ACIE – ACIS1 ACIS0 page 108

0x07 ADMUX REFS1 REFS0 ADLAR REFS2 MUX3 MUX2 MUX1 MUX0 page 123

0x06 ADCSRA ADEN ADSC ADATE ADIF ADIE ADPS2 ADPS1 ADPS0 page 124

0x05 ADCH ADC Data Register High Byte page 126

0x04 ADCL ADC Data Register Low Byte page 126

0x03 ADCSRB BIN ACME IPR – – ADTS2 ADTS1 ADTS0 page 108, page 126

0x02 Reserved –

0x01 Reserved –

0x00 Reserved –

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory

addresses should never be written.

2. I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In these

registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

3. Some of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI

instructions will only operation the specified bit, and can therefore be used on registers containing such Status Flags. The

CBI and SBI instructions work with registers 0x00 to 0x1F only.

Loading...

Loading...