176

7679H–CAN–08/08

AT90CAN32/64/128

nal, ensuring sufficient time for data signals to stabilize. This is clearly seen by summarizing

Table 16-2 and Table 16-3, as done below:

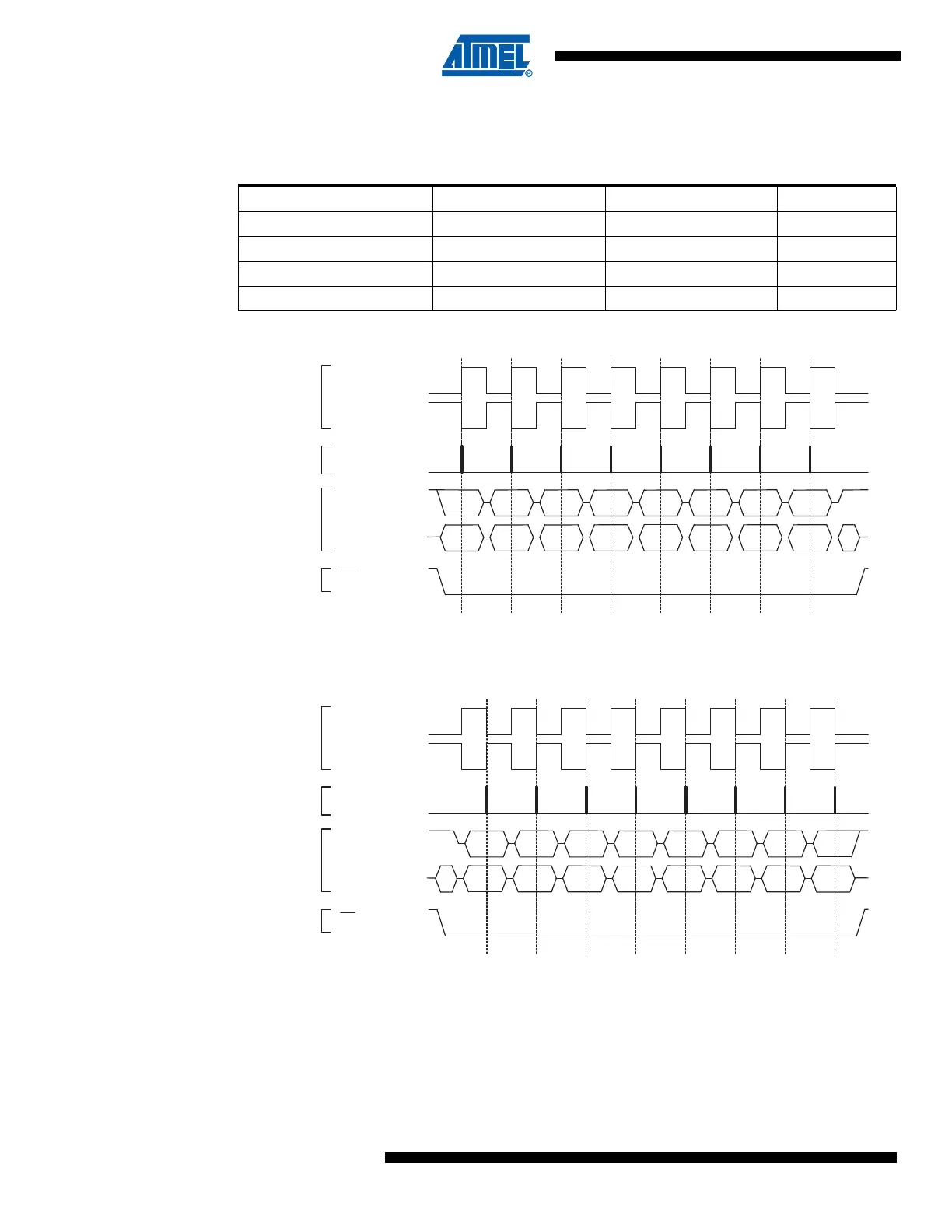

Figure 16-3. SPI Transfer Format with CPHA = 0

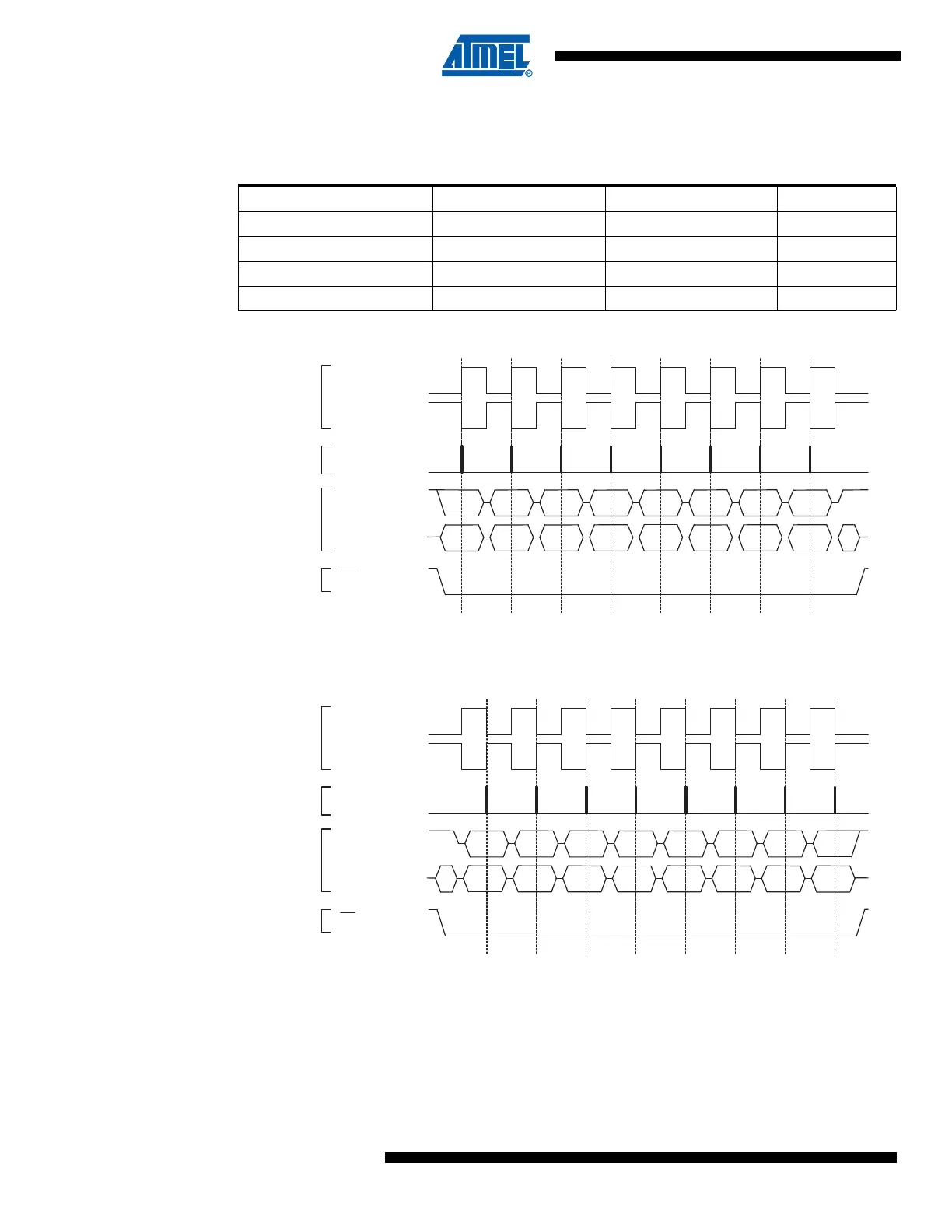

Figure 16-4. SPI Transfer Format with CPHA = 1

Table 16-5. CPOL Functionality

Leading Edge Trailing Edge SPI Mode

CPOL=0, CPHA=0 Sample (Rising) Setup (Falling) 0

CPOL=0, CPHA=1 Setup (Rising) Sample (Falling) 1

CPOL=1, CPHA=0 Sample (Falling) Setup (Rising) 2

CPOL=1, CPHA=1 Setup (Falling) Sample (Rising) 3

Bit 1

Bit 6

LSB

MSB

SCK (CPOL = 0)

mode 0

SAMPLE I

MOSI/MISO

CHANGE 0

MOSI PIN

CHANGE 0

MISO PIN

SCK (CPOL = 1)

mode 2

SS

MSB

LSB

Bit 6

Bit 1

Bit 5

Bit 2

Bit 4

Bit 3

Bit 3

Bit 4

Bit 2

Bit 5

MSB first (DORD = 0)

LSB first (DORD = 1)

SCK (CPOL = 0)

mode 1

SAMPLE I

MOSI/MISO

CHANGE 0

MOSI PIN

CHANGE 0

MISO PIN

SCK (CPOL = 1)

mode 3

SS

MSB

LSB

Bit 6

Bit 1

Bit 5

Bit 2

Bit 4

Bit 3

Bit 3

Bit 4

Bit 2

Bit 5

Bit 1

Bit 6

LSB

MSB

MSB first (DORD = 0)

LSB first (DORD = 1)

Loading...

Loading...