MSC SM2S-IMX8MINI 34 / 87

User Manual

Features:

• Single-Link and Dual-Link with four data lanes per link

• Supports 18bpp and 24bpp

• Pixel clock up to 154 MHz

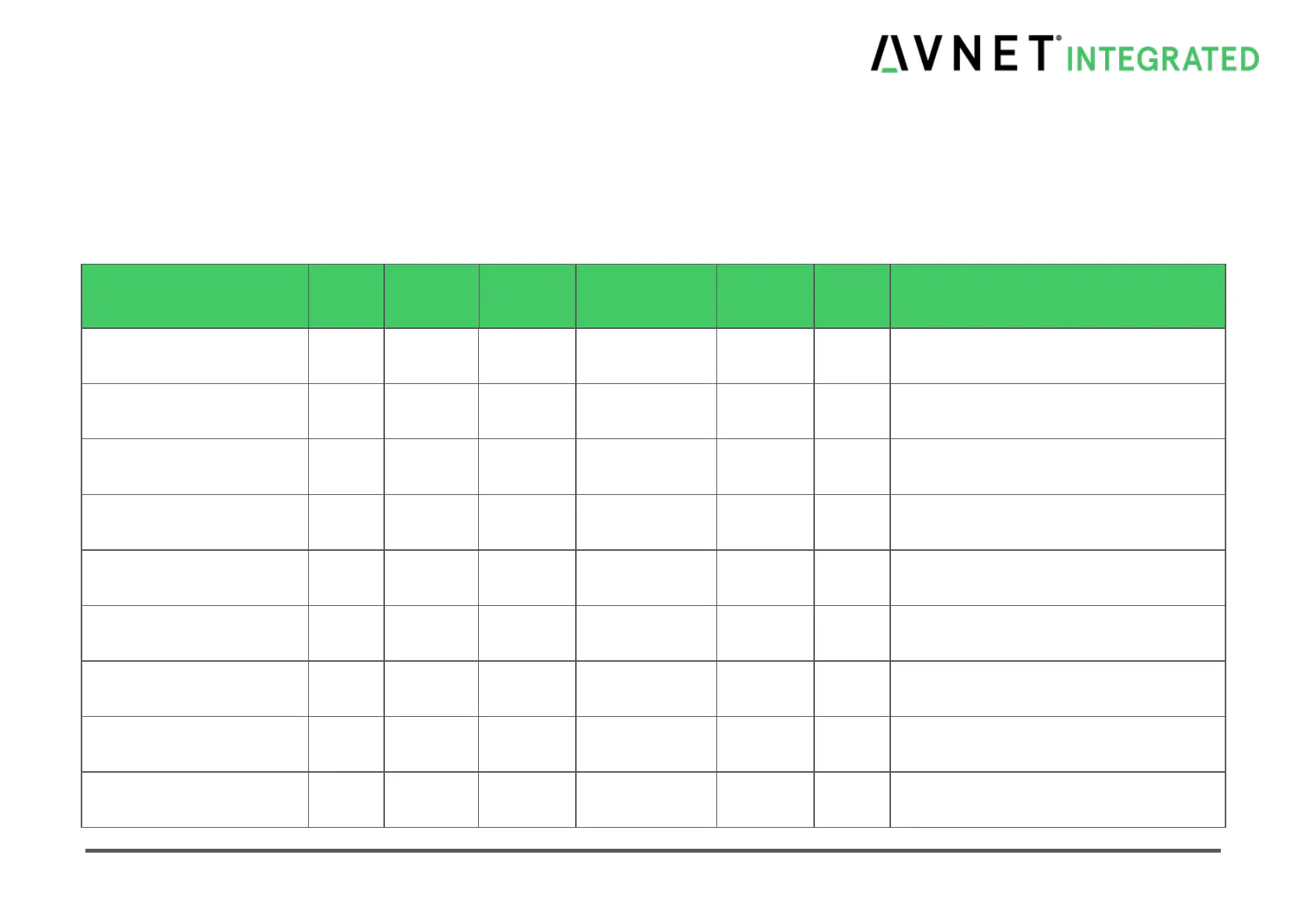

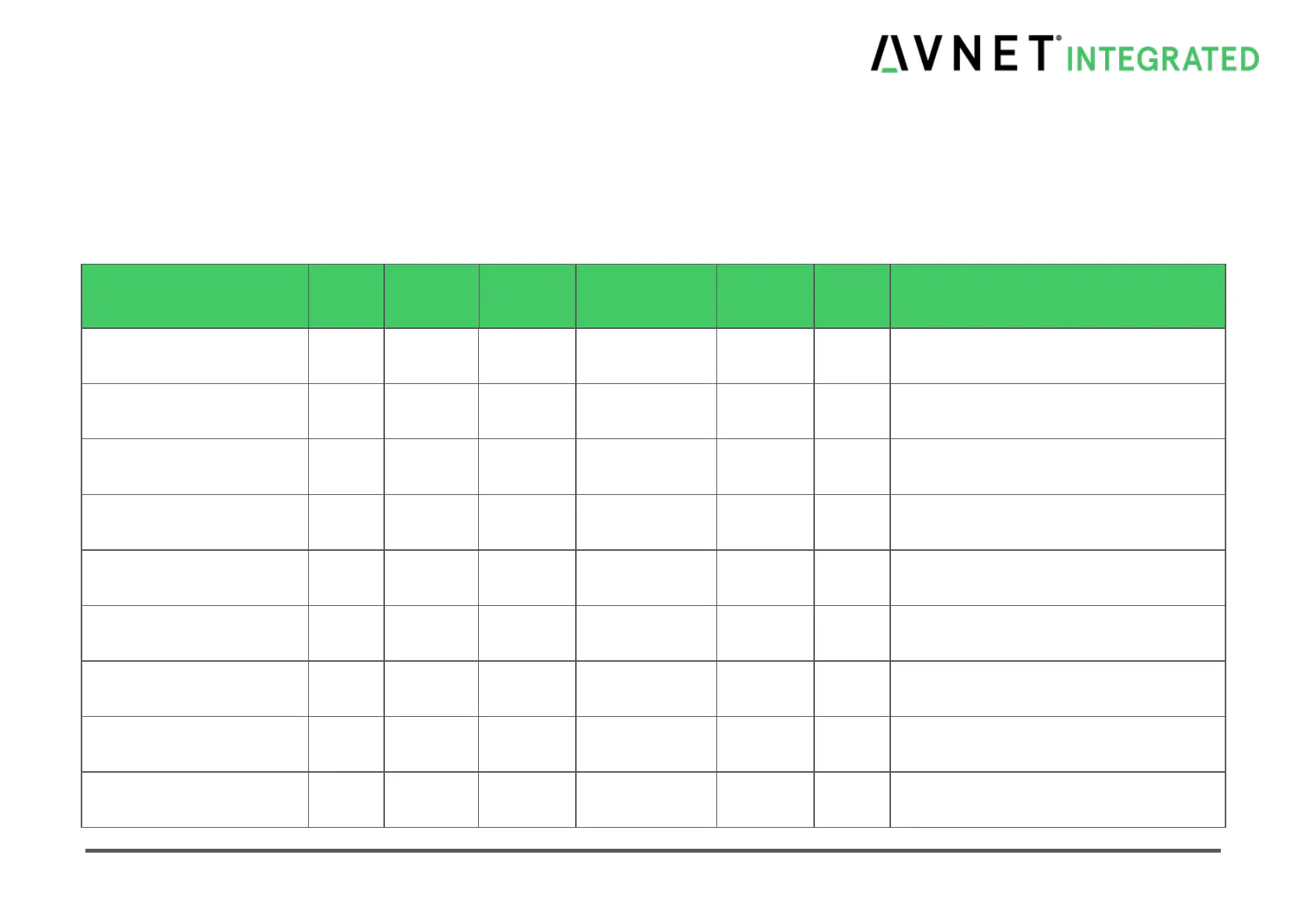

Table 11: LVDS Signal Description

LVDS0_0+ / DSI0_D0+

LVDS0_0- / DSI0_D0-

LVDS Channel 0 differential pair

LVDS0_1+ / DSI0_D1+

LVDS0_1- / DSI0_D1-

LVDS Channel 0 differential pair

LVDS0_2+ / DSI0_D2+

LVDS0_2- / DSI0_D2-

LVDS Channel 0 differential pair

LVDS0_3+ / DSI0_D3+

LVDS0_3- / DSI0_D3-

LVDS Channel 0 differential pair

LVDS0_CK+ / DSI0_CLK+

LVDS0_CK- / DSI0_CLK+

LVDS Channel 0 differential clock

LVDS1_0+ / DSI1_D0+

LVDS1_0- / DSI1_D0-

LVDS Channel 1 differential pair

LVDS1_1+ / DSI1_D1+

LVDS1_1- / DSI1_D1-

LVDS Channel 1 differential pair

LVDS1_2+ / DSI1_D2+

LVDS1_2- / DSI1_D2-

LVDS Channel 1 differential pair

LVDS1_3+ / DSI1_D3+

LVDS1_3- / DSI1_D3-

LVDS Channel 1 differential pair

Loading...

Loading...