- 71 -

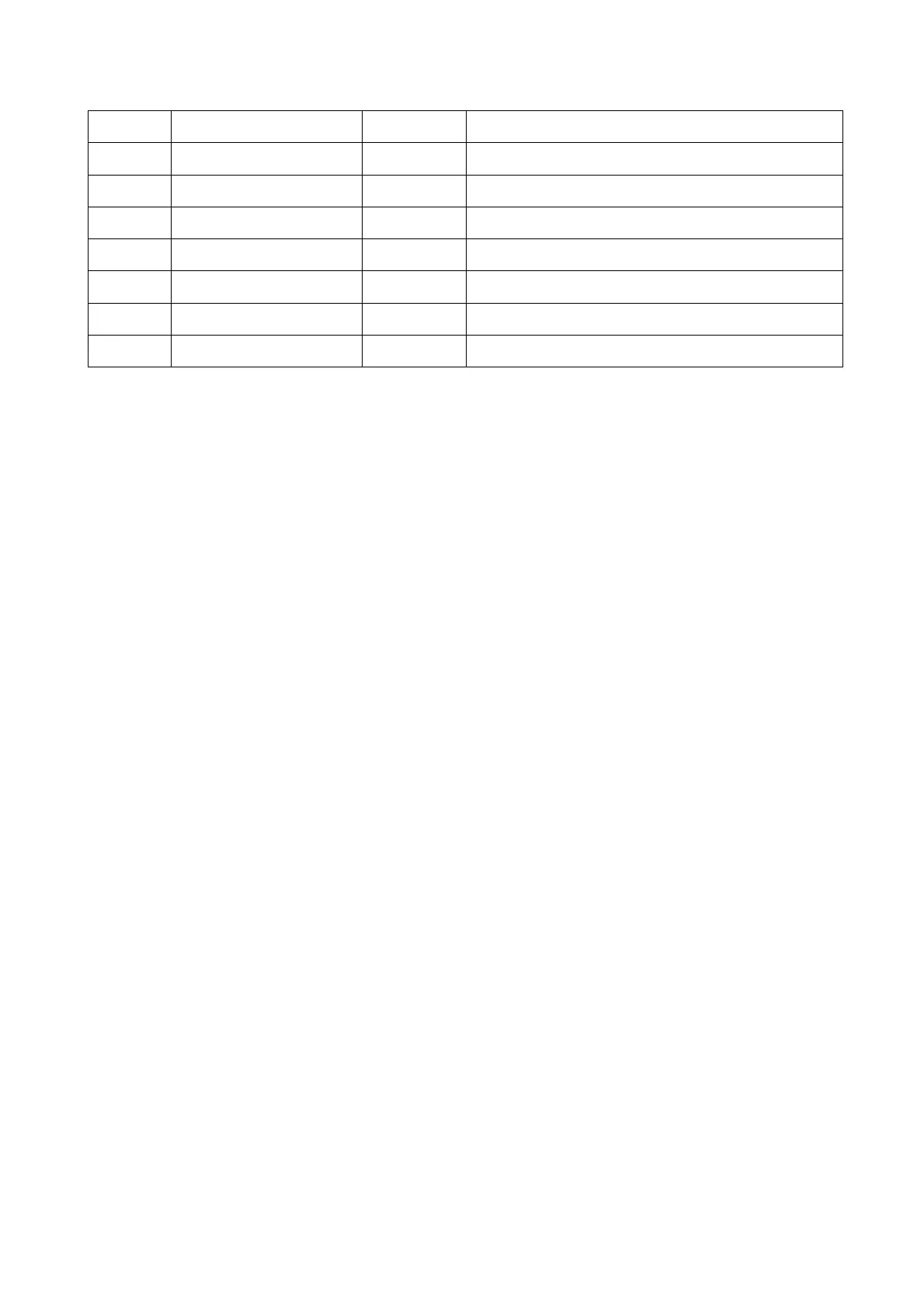

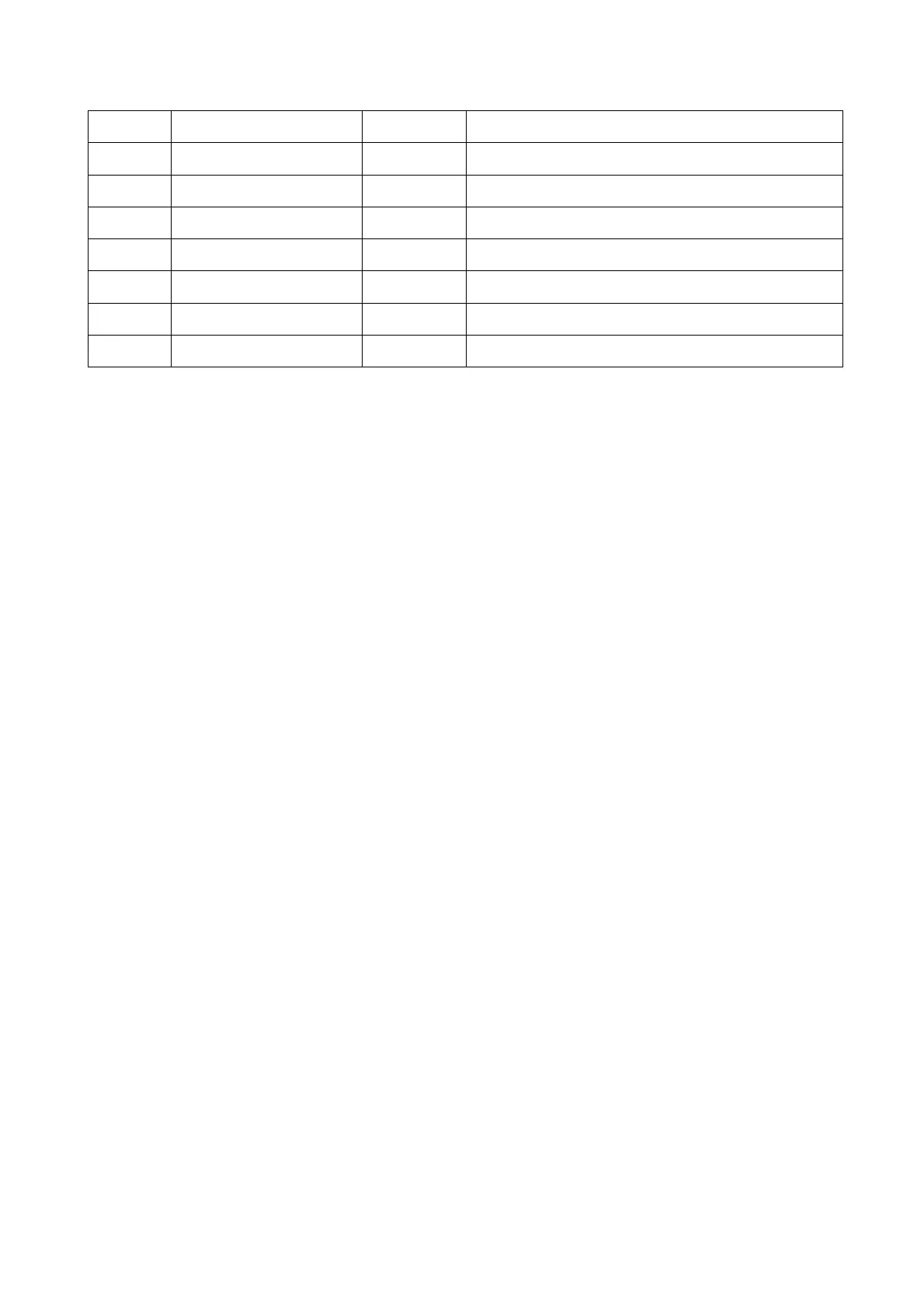

PIN No Symbol I/O

Description

1 1OUT O

Output 1

2 1IN– I

Inverting Input Pin 1

3 1IN+ I

Non-Inverting Input Pin 1

4 VCC– I

Negative Power Supply

5 2IN+ I

Non-Inverting Input Pin 2

6 2IN– I

Inverting Input Pin 2

7 2OUT O

Output 2

3.5.7 function introduction to CD4052

1. Description

The CD4052B analog multiplexers is digitally-controlled analog switches having low ON impedance and

very low OFF leakage current. Control of analog signals up to 20VP-P can be achieved by digital signal

amplitudes of 4.5V to 20V (if VDD-VSS = 3V, a VDD-VEE of up to 13V can be controlled; for VDD-VEE level

differences above 13V, a VDD-VSS of at least 4.5V is required). For example, if VDD = +4.5V, VSS = 0V, and

VEE = -13.5V, analog signals from -13.5V to +4.5V can be controlled by digital inputs of 0V to 5V. These

multiplexer circuits dissipate extremely low quiescent power over the full VDD-VSS and VDD-VEE

supply-voltage ranges, independent of the logic state of the control signals. When a logic “1” is present at the

inhibit input terminal, all channels are off.

The CD4052B is a differential 4-Channel multiplexer having two binary control inputs, A and B, and an

inhibit input. The two binary input signals select 1 of 4 pairs of channels to be turned on and connect the

analog inputs to the outputs.

2. FEATURES

◆ Wide Range of Digital and Analog Signal Levels

Digital : 3V to 20V

Analog: ≤20VP-P

◆ Low ON Resistance, 125W (Typ) Over 15VP-P Signal Input Range for V

DD

-V

EE

= 18V

◆ High OFF Resistance, Channel Leakage of ±100pA (Typ) at V

DD

-V

EE

= 18V

◆ Logic-Level Conversion for Digital Addressing Signals of 3V to 20V (V

DD

-V

SS

= 3V to 20V) to Switch

Analog Signals to 20VP-P (V

DD

-V

EE

= 20V)

◆ Matched Switch Characteristics, r

ON

= 5W (Typ) for V

DD

-V

EE

= 15V

◆ Very Low Quiescent Power Dissipation Under All Digital-Control Input and Supply Conditions, 0.2mW

(Typ) at V

DD

-V

SS

= V

DD

-V

EE

= 10V

◆ Binary Address Decoding on Chip

◆ 5V, 10V and 15V Parametric Ratings

Loading...

Loading...