Cavli Wireless C100QM/C10QM Hardware Manual

60

possible interference lines.

✧ The spacing between the SDIO signal and other signals needs to be greater than 2

times the line width and ensure that the bus load is less than 40pF;

✧ Add a pull-up resistor to the SDIO signal with a resistance range of 10~100kΩ, a

recommended value of 100kΩ, and pull up to the VDD_SDIO pin of the module.

✧ To ensure good ESD performance, it is recommended to add a TVS tube to the SD

card pin and place it near the pin.

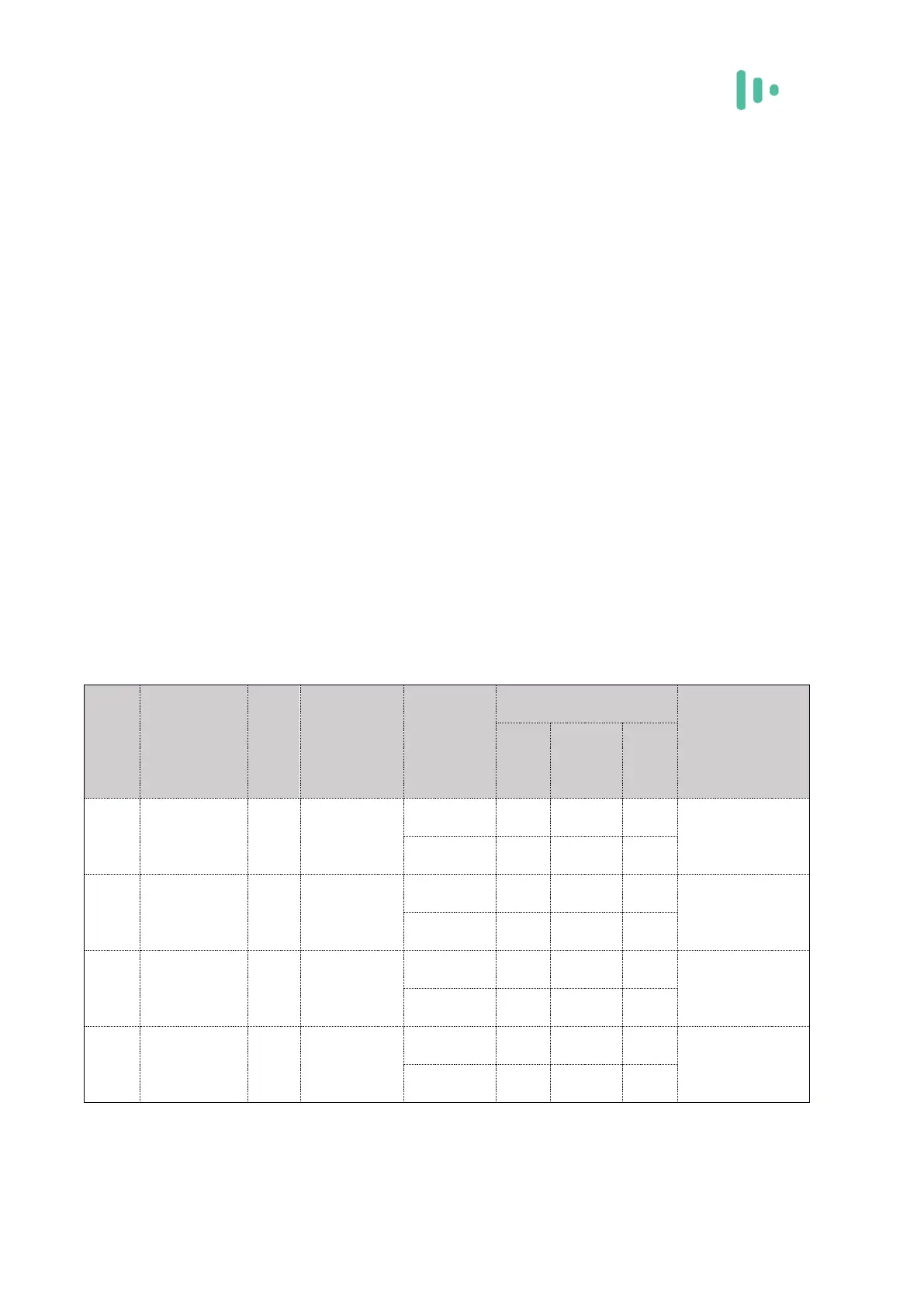

3.14 SPI interface / multiplexed I2S interface

The C100QM/C10QM provides an SPI interface with a maximum clock rate of 50MHz. In

addition, the module can only be used as the master, and the interface voltage domain is

1.8V.

Table 3-20 SPI Pin Definitions

Loading...

Loading...