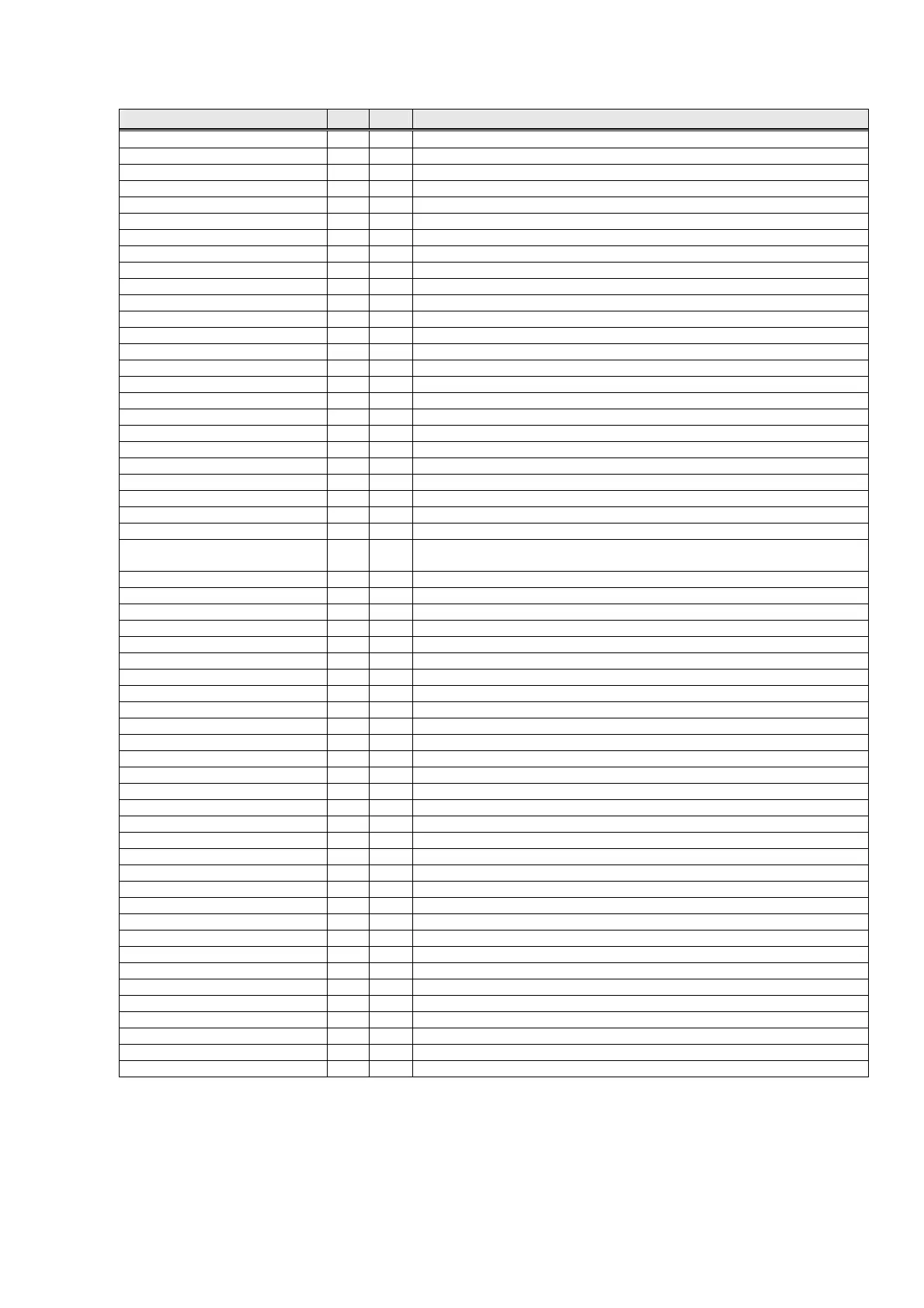

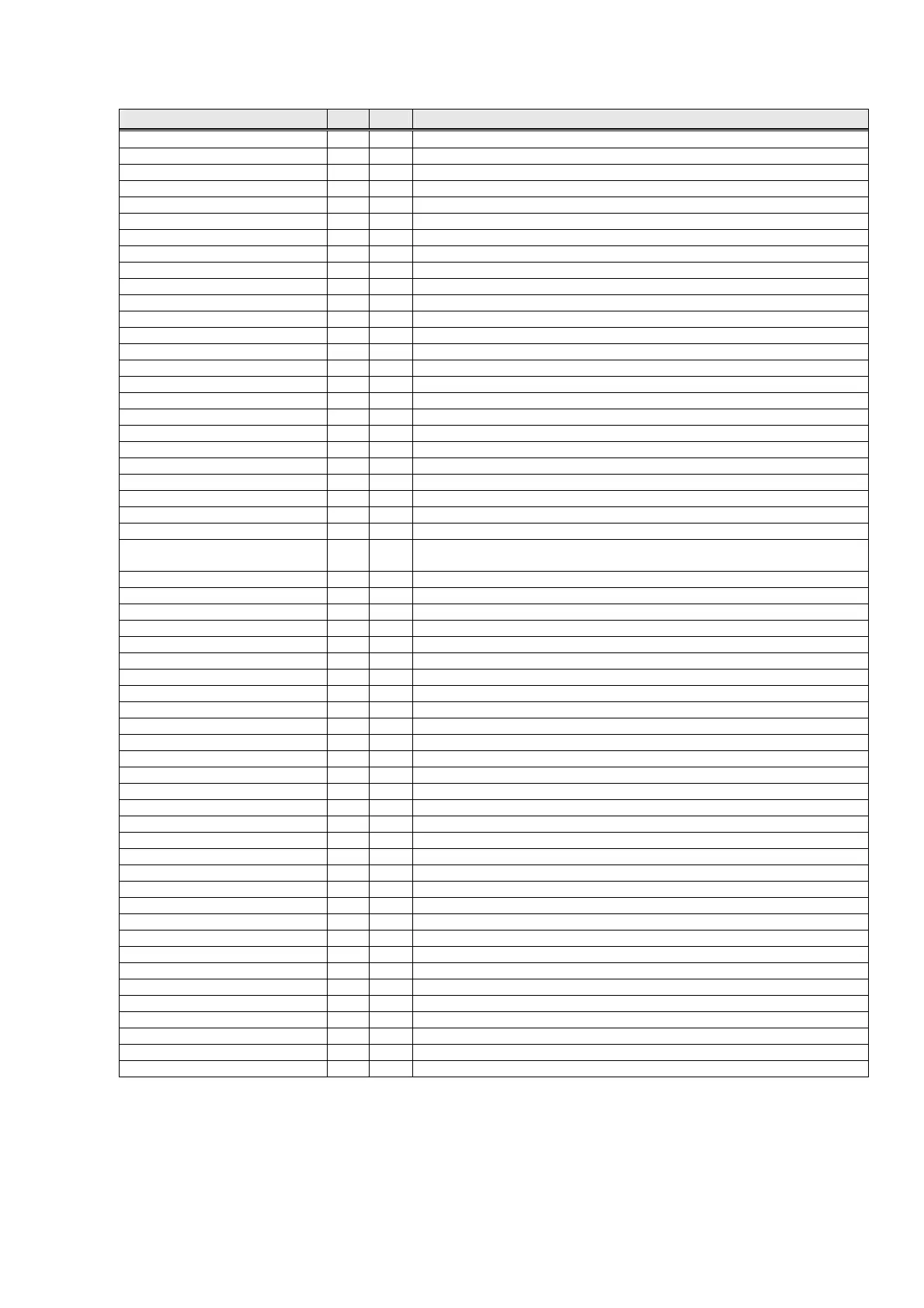

171

Signal Name Pin# Type Description – TCC8600

GPIO_A[15] / EXINT[3] 123 I/O GPIO_A[15] / External Interrupt Request [3]

GPIO_A[14] / EXINT[2] 122 I/O GPIO_A[14] / External Interrupt Request [2]

GPIO_A[13] / EXINT[1] 121 I/O GPIO_A[13] / External Interrupt Request [1]

GPIO_A[12] / EXINT[0] 120 I/O GPIO_A[12] / External Interrupt Request [0]

GPIO_A[11] 117 I/O GPIO_A[11] / I2C Clock / GPSB/GSIO3 Data In

GPIO_A[10] 116 I/O GPIO_A[10] / I2C Data Line / GPSB/GSIO3 FRM

GPIO_A[9] 115 I/O GPIO_A[9] / I2C Clock./ Bus Width (BW) / GPSB/GSIO3 Clock

GPIO_A[8] 114 I/O GPIO_A[8] / I2C Data Line / GPSB/GSIO3 Data Output

GPIO_A[7] 113 I/O GPIO_A[7] / GPSB/GSIO1 Data In

GPIO_A[6] 112 I/O GPIO_A[6] / GPSB/GSIO1 FRM

GPIO_A[5] 111 I/O GPIO_A[5] / GPSB/GSIO1 Clock

GPIO_A[4] 109 I/O GPIO_A[4] / GPSB/GSIO1 Data Output

GPIO_A[3] / CDAI 108 I/O CD Data Input / GPIO_A[3] / GPSB/GSIO1 Data In

GPIO_A[2] / CLRCK 107 I/O CD Data Word Clock Input / GPIO_A[2] / GPSB/GSIO1 FRM

GPIO_A[1] / CBCLK 106 I/O CD Data Bit Clock Input / GPIO_A[1] / GPSB/GSIO1 Clock

GPIO_A[0] / SPDIFTX 105 I/O GPIO_A[0] / SPDIF TX Output / GPSB/GSIO1 Data Output

GPIO_B[25] / DAI 90 I/O I2S Digital Audio data Input / GPIO_B[25]

GPIO_B[24] / DAO 89 I/O I2S Digital Audio data Output / GPIO_B[24] / Boot Mode Bit 2 (BM[2])

GPIO_B[23] / MCLK 88 I/O I2S System Clock / GPIO_B[23]

GPIO_B[22] / LRCK 87 I/O I2S Word Clock / GPIO_B[22] / Boot Mode Bit 1 (BM[1])

GPIO_B[21] / BCLK 86 I/O I2S Bit Clock / GPIO_B[21] / Boot Mode Bit 0 (BM[0])

GPIO_B[9] / UART0RXD 63 I/O GPIO_B[9] / UART0 RX Data

GPIO_B[8] / UART0TXD 62 I/O GPIO_B[8] / UART0 TX Data

GPIO_B[6] / IDE_nCS1 60 I/O GPIO_B[6] / Chip select 1 for IDE Interface. Internal pull-up resistor enabled at reset.

GPIO_D[21] 99 I/O GPIO_D[21]. Internal pull-up resistor enabled at reset.

GPIO_D[20] / UART1RTSn 98 I/O

GPIO_D[20] / UART1 RTS Output (active low). Internal pull-up resistor enabled at

reset.

GPIO_D[19] / UART1RXD 96 I/O GPIO_D[19] / UART1 RX Data. Internal pull-up resistor enabled at reset.

GPIO_D[18] / UART1TXD 95 I/O GPIO_D[18] / UART1 TX Data. Internal pull-up resistor enabled at reset.

GPIO_D[17] 94 I/O GPIO_D[17] / I2C SCL

GPIO_D[16] 93 I/O GPIO_D[16] / I2C SDA

GPIO_D[15] / UART1CTSn 92 I/O GPIO_D[15] / UART1 CTS Input (active low)

ADIN0 68 AI General purpose multi-channel ADC input 0

ADIN2 67 AI General purpose multi-channel ADC input 2

ADIN4 66 AI General purpose multi-channel ADC input 4

XIN 55 I 12MHz Crystal Oscillator Input. Voltage must not exceed VDDI (1.95V).

XOUT 54 O 12MHz Crystal Oscillator Output

XTIN 57 I 32.768kHz Crystal Oscillator Input.Voltage must not exceed VDDI (1.95V).

XTOUT 56 O 32.768kHz Crystal Oscillator Output

XFILT 75 AO PLL0 filter output. 350pF capacitor is required.

XFILT1 72 AO PLL1 filter output. 1200pF capacitor is required.

TDI / GPIO_J[1] 100 I/O JTAG serial data input. Internal pull-up resistor is enabled at reset

TMS / GPIO_J[2] 101 I/O JTAG test mode select. Internal pull-up resistor is enabled at reset

TCK / GPIO_J[3] 102 I/O JTAG test clock. Internal pull-up resistor is enabled at reset

TDO / GPIO_J[0] 103 I/O JTAG serial data output. Internal pull-up resistor is enabled at reset

nTRST / GPIO_J[4] 104 I/O JTAG reset signal. Active low.. Internal pull-up resistor is enabled at reset

MODE1 78 I Mode Setting Input 1. Pull-down for normal operation.

nRESET 77 I System Reset. Active low.

VDDIO 9 PWR Digital Power for I/O (3.3V)

VDDIO 26 PWR Digital Power for I/O (3.3V)

VDDIO 43 PWR Digital Power for I/O (3.3V)

VDDIO 65 PWR Digital Power for I/O (3.3V)

VDDIO 85 PWR Digital Power for I/O (3.3V)

VDDIO 119 PWR Digital Power for I/O (3.3V)

VDDUSB 84 PWR Power for USB I/O (3.3V)

VDDI 7 PWR Digital Power for Internal Core (1.8V)

VDDI 24 PWR Digital Power for Internal Core (1.8V)

VDDI 40 PWR Digital Power for Internal Core (1.8V)

Loading...

Loading...