Troubleshooting with software

31

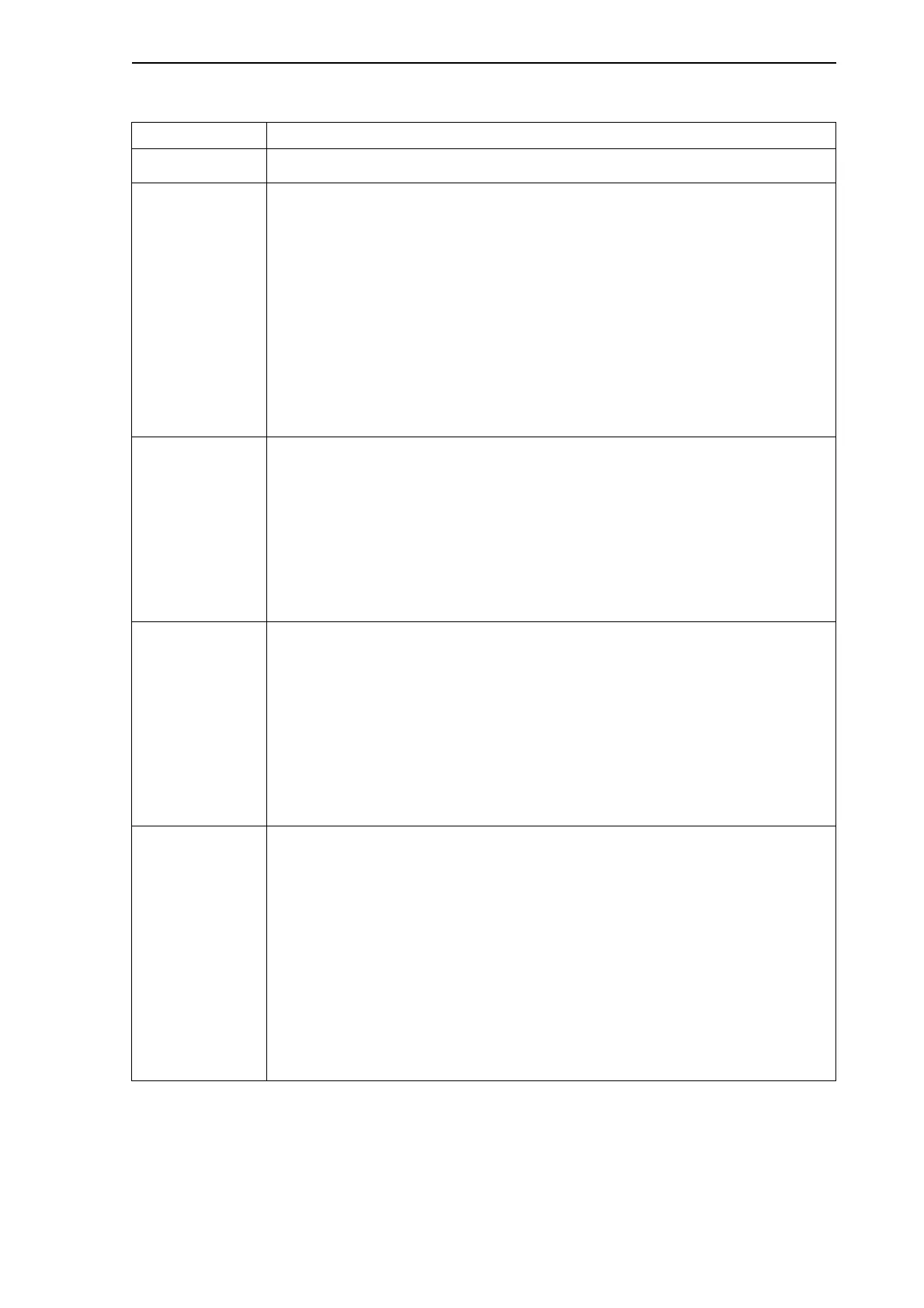

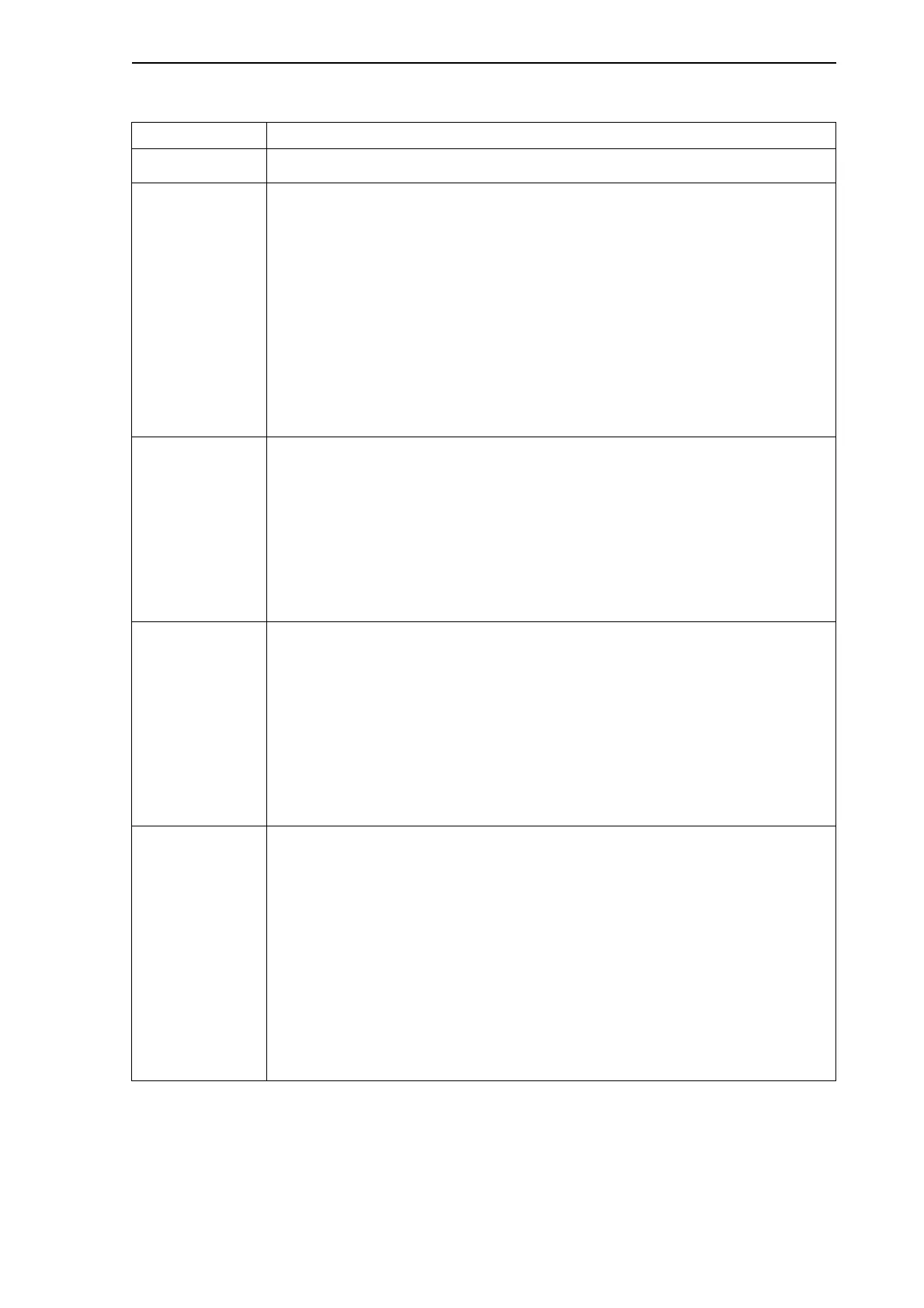

Table 5.3: Addresses and contents of input ports

Address Contents

0x00-0x3f Z180 microprocessor internal registers

0x80 FPGA Memory Controller register

The Memory Controller chooses whether Traffic Memory, FLASH or

Shared Memory is visible at the physical address space C0000 - FFFFF.

The Default memory is Shared Memory.

Bit 2: when set to 1: FLASH, when 0: Shared Memory

Bit 3: when set to 1: Traffic Memory, when 0: SM/FLASH

Bit 5: when set to 1 adds two (2) wait states to SM, TM and FLASH

addressings

Bit 6: when set to 1 adds three (3) wait states to SM, TM and FLASH

addressings

Bit 7: The interchange of Traffic Memory’s and Shared Memory’s AM code

0x81 FPGA Ctrl_A register:

Bit 0: Controls the green status LED

Bit 1: When set to 1, causes the Z180 CPU to reset

Bit 2: When set to 0, activates the VME SysFail signal

Bit 3: Enables the Zilog NMI (ACFAIL)

Bit 4:Tests the NMI interrupt

Bit 5: Controls the yellow status LED

Bits 6 and 7: Control the red status LED

0x82 FPGA Ctrl_B register:

Bit 0: Refreshes hardware watchdog

Bit 1: Enables the Zilog interrupt INT1

Bit 2: Enables the Zilog interrupt INT2

Bit 3: Automatically refreshes the hardware watchdog

Bit 4: When set to 1, invokes outbound VME interrupt

Bit 5: Disables the VME INT1 (1=disabled)

Bit 6: Tests the INT1 interrupt (1=on, 0=off)

Bit 7: Tests the INT2 interrupt (1=on, 0=off)

0x84 FPGA MVB Signal Status register:

You can read the statuses of the system signals from this register. If

inbound SYSRESET is active, there might be a failure with the Watchdog

arrangement. If inbound SYSFAIL is active, there is a fault with another

module in the system, or the self tests at start-up are still taking place. The

inbound SYSFAIL can be used to synchronize the system startup.

Bit 0: The ’emulator-jumper’ is installed (1=no emulator)

Bits 1-4: Bits used for identifying the hardware configuration

Bit 5: If "1" no EMD FGPA required (should be always "1")

Bit 6: VME SYSFAIL signal active

Bit 7: VME ACFAIL signal active

Loading...

Loading...