14. Functions

RX8130CE Jump to Top / Bottom

ETM50E-07 Seiko Epson Corporation 28

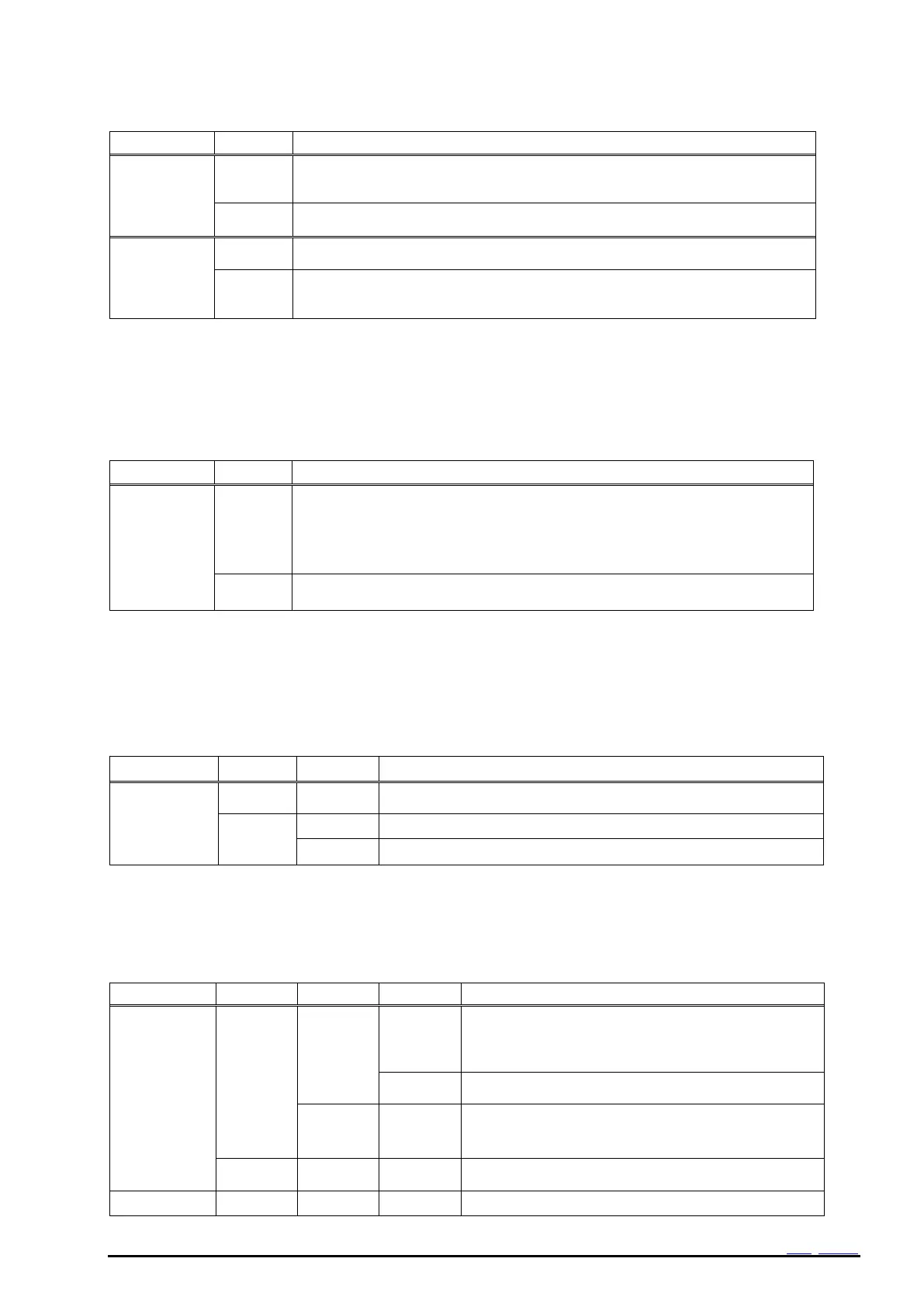

Table 18 Wakeup timer interrupt detection flag

The TF bit is cleared to zero to prepare for the next status detection

Clearing this bit to zero does not enable the /IRQ low output status to be cleared (to Hi-z).

Invalid (writing a 1 will be ignored)

Wakeup timer interrupt events are detected.

(Result is retained until this bit is cleared to zero.)

5) TIE bit(Timer Interrupt Enable)

This bit is used to control output of interrupt signals from the /IRQ pin when a wakeup timer interrupt

event has occurred.

Table 19 Wakeup timer interrupt control

1) When a wakeup timer interrupt event occurs, an interrupt signal is not

generated.

2) When a wakeup timer interrupt event occurs, the interrupt signal is canceled

(/IRQ status changes from low to Hi-z).

When a wakeup timer interrupt event occurs, an interrupt signal is generated

(/IRQ status changes from Hi-z to low).

6) TBKON, TBKE bit

This function selects the operation time with the main power supply or the operation time with the

backup power supply. The count value is added.

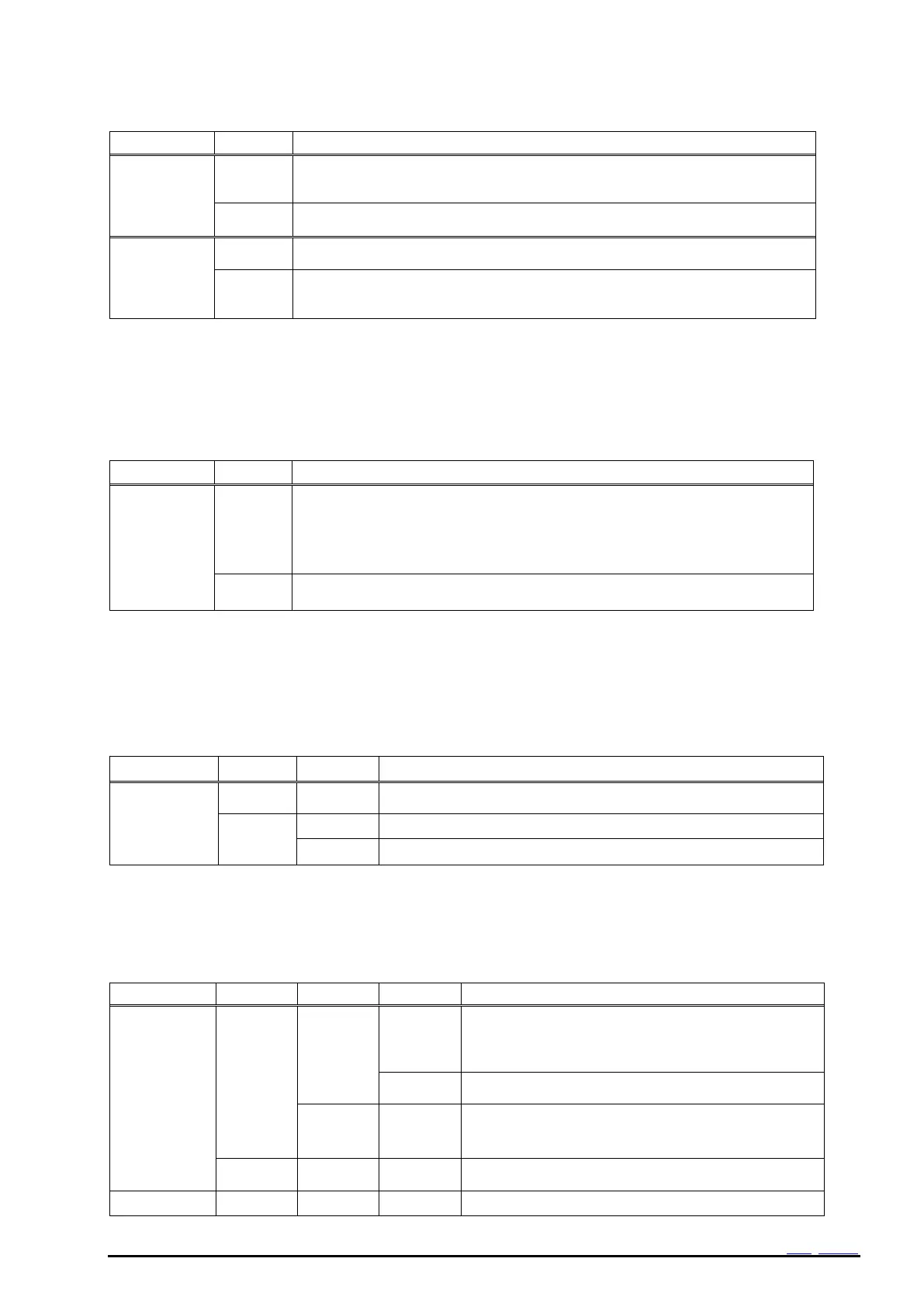

Table 20 Wakeup timer normal mode/backup mode control

This setting counts normal mode and backup mode.

This setting counts it at time of normal mode(VDD operation)

This setting counts it at time of backup mode (VBAT operation)

7) TSTP bit (Timer Stop)

This bit is used to stop wakeup timer count down.

Table 21 Wakeup timer stop control

Writing a "0" to this bit cancels stop status (restarts

timer count down).

The reopening value of the countdown is a

stopping value

Setting of TSTP value becomes invalid, and the

count does not stop even if set it in TSTP="1".

The count stops at the time of the setting of 64 Hz,

1 Hz,1/60 Hz,1/3600 Hz.

It doesn’t start counting

Loading...

Loading...