TV?

N

[r

N

TPI

•

TP2

TP3

.

?

*

9

m

U

I

-

b

b

??

OC20Q

Q-

R55

Ul1

mm-

Ll

u

-l

I1

I

TOIFROM BLOCK

I

F

23 LZMRQ

'I1

NOT USED

30 GND DIG

1

GNDDIG

BDl

BDQ

803

802

Figure

8-57.

A7

Marker, Test Points

1

thru

3

I

11

I

BAl

BAQ

BA3

BA2

Figure 8-56.

A7

Marker, Component Locations

0

Vdc

NOTES

AMPLITUDE

DECREASES

WlTH LONGER

SWEEP TIME

I

GND ANLG

GND ANLG

NOT USED

NOT USED

THE FOLLOWING KEY ENTRIES PROVIDE FRONT PANEL ACCESS FOR A DATA

WRITE/READ

OPERATION TOIFROM THE ADDRESSED LOCATION:

11111111111111

I

Ill

AMPLITUDE

DECREASES

WITH SWEEP LONGER TIME

FUNCTION KEY ENTRY

I

I

I-

-1

I

--

28 pec

I

-40 pec

I

I

I

LEN 1

I

I

11

I

I

'Hex Address Entry SHIFT 0

0

(enter hex address)

Hex Data WRITE M2 (enter data: two hex digits)

Hex Data READ M3

Hex Data Rotation Write M4

Hex Addressed Fast Read M5

L RFON

I

IN

LEN 2

I

t

,

I

I

I

I

I

OSC BIAS 0 UT

L RFM IN

L SSRQ IN

SQ MOD IN

A6P1-23

P2-26

NOT USED

'TO ADDRESS A DIFFERENT LOCATION, PRESS

MI AND ENTER THE NEW ADDRESS, OR

USE

THE

INCREMENT

KEYS

r

.s

TO

STEPTO

THE

NEW ADDRESS.

LEN 3

I

I

I

!

I

TO PREVENT THE MICROPROCESSOR FROM SERVICING THE RETRACE

INTERRUPT, PRESS

8350A CW

.

43 PULSEIN

I

N J5(BNC) D

22 L BQSW2 NOT USED

44 +5V REG IN

A9P1-7 K

Figure

8-59.

A

7

Address Decoder Timing Diagram

Figure 8-58.

A7

Delay Compensation, Test Points

4

thru 6

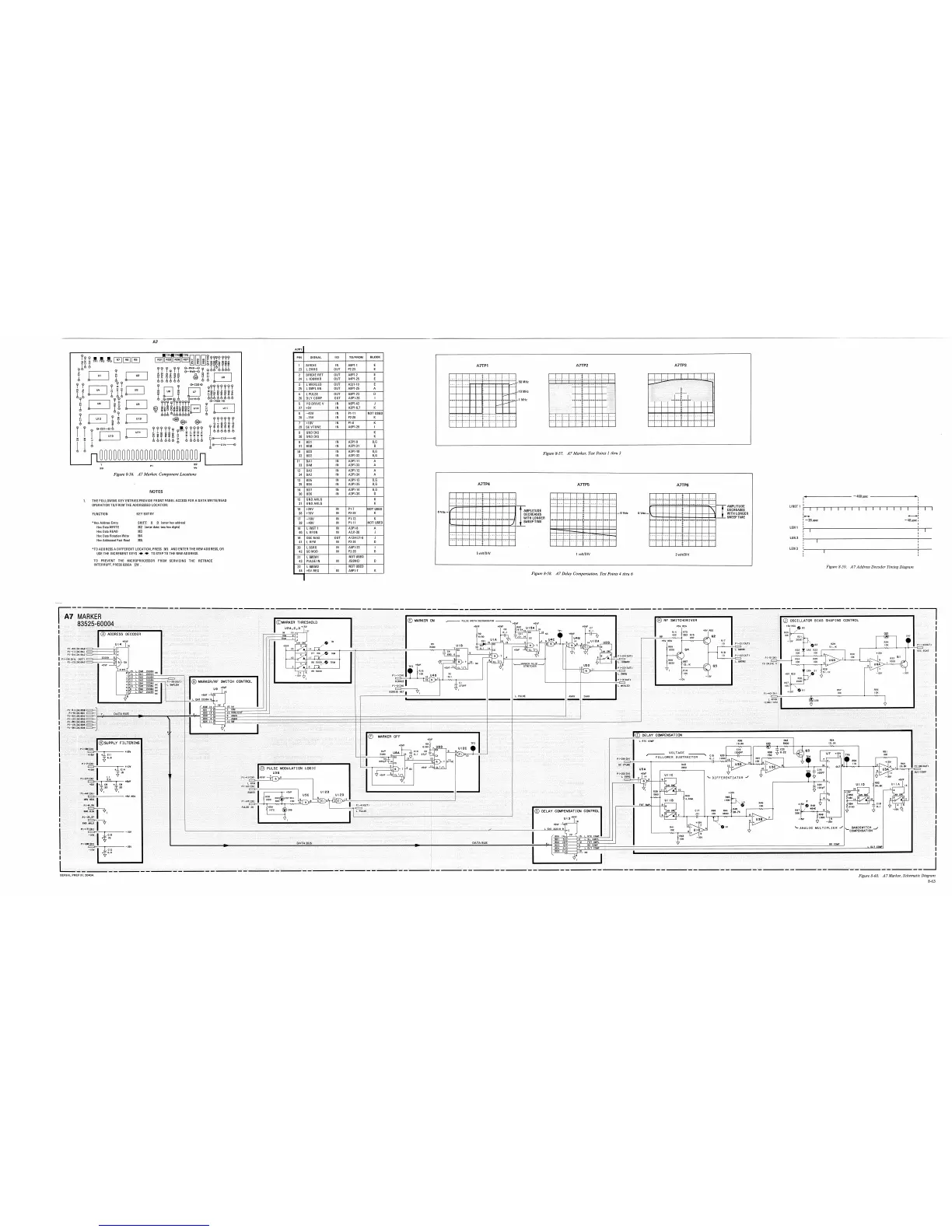

SERIAL PREFIX: 2040A

Figure

8-60.

A

7

Marker, Schematic Diagram

8-63

Loading...

Loading...