User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_03.fm.(1.2)

March 27, 2006

Instruction-Cache and Data-Cache Operation

Page 123 of 377

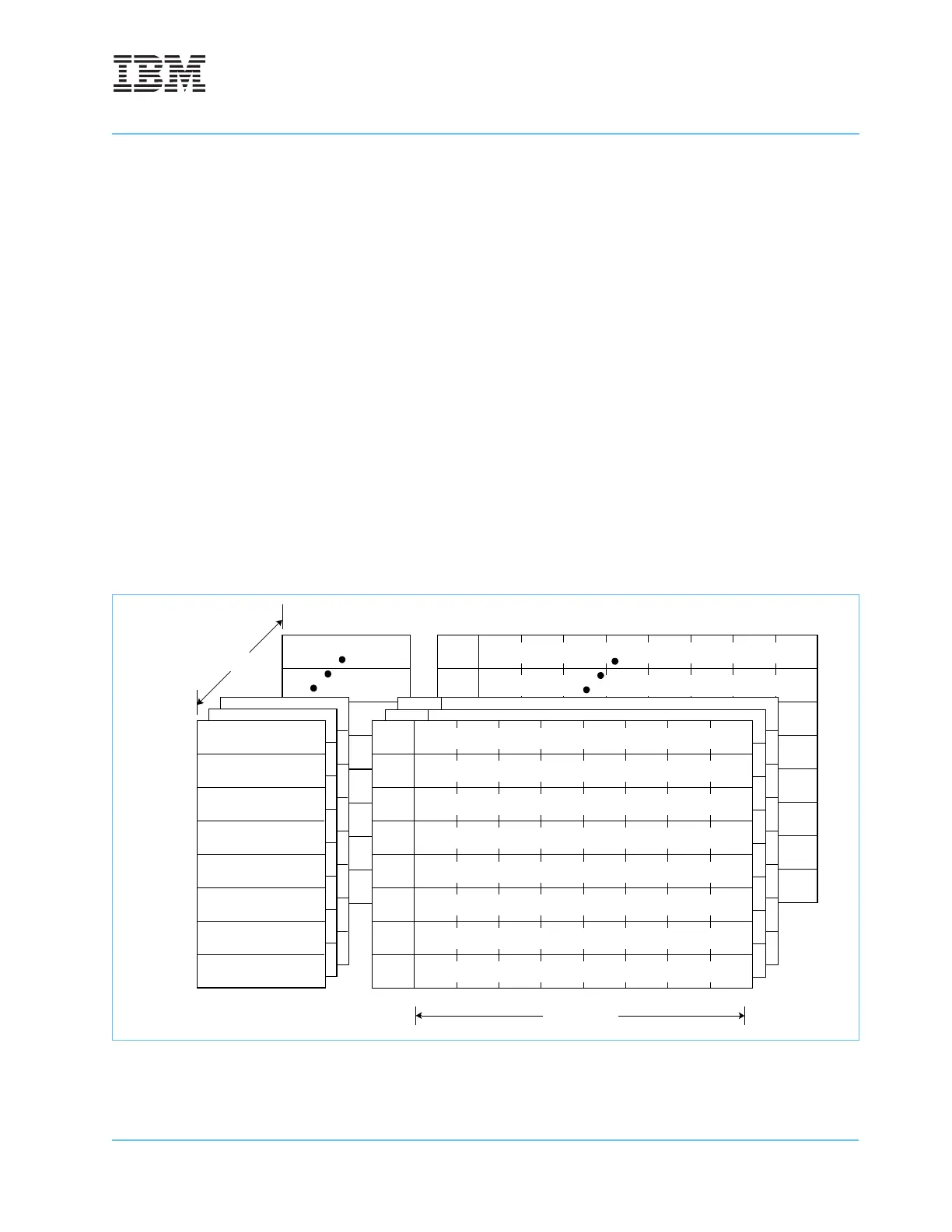

3.1 Data-Cache Organization

The data cache is organized as 128 sets of eight ways as shown in Figure 3-2. Each way consists of 32

bytes, two state bits, and an address tag. Note that in the PowerPC Architecture, the term ‘cache block,’ or

simply ‘block,’ when used in the context of cache implementations, refers to the unit of memory at which

coherency is maintained. For the 750GX, this is the 8-word (32-byte) cache line. This value might be different

for other PowerPC implementations.

Each cache block contains eight contiguous words from memory that are loaded from an 8-word boundary

(that is, bits A[27–31] of the logical (effective) addresses are zero). As a result, cache blocks are aligned with

page boundaries. Note that address bits A[20–26] provide the index to select a cache set. Bits A[27–31]

select a byte within a block. The two state bits implement a 3-state MEI protocol, a coherent subset of the

standard 4-state modified/exclusive/shared/invalid (MESI) protocol. The MEI protocol is described in

Section 3.3.2 on page 126.

The tags consist of physical address bits PA[0–19]. Address translation occurs in parallel with set selection

(from A[20–26]), and the higher-order address bits (the tag bits in the cache) are physical.

The 750GX’s on-chip data-cache tags are single-ported, and load or store operations must be arbitrated with

snoop accesses to the data-cache tags. Load or store operations can be performed to the cache on the clock

cycle immediately following a snoop access if the snoop misses; snoop hits might block the data cache for

two or more cycles, depending on whether a copy-back to main memory is required.

Figure 3-2. Data-Cache Organization

8 Words/Block

128 Sets

Way 5

Way 6

Way 7

Way 4

Address Tag 4

Address Tag 5

Address Tag 6

Address Tag 7

Way 1

Way 2

Way 3

Way 0

Address Tag 0

Address Tag 1

Address Tag 2

Address Tag 3

State

State

State

Words [0–7]

State

Words [0–7]

Words [0–7]

Words [0–7]

State

State

State

Words [0–7]

State

Words [0–7]

Words [0–7]

Words [0–7]

Loading...

Loading...