User’s Manual

IBM PowerPC 750GX and GL RISC Microprocessor

gx_04.fm.(1.2)

March 27, 2006

Exceptions

Page 157 of 377

4.3.2 Machine Status Save/Restore Register 1 (SRR1)

SRR1 is used to save machine status (selected MSR bits and possibly other status bits as well) on excep-

tions and to restore those values when a Return from Interrupt (rfi) instruction is executed.

When the 750GX takes a machine-check exception, it will set one or more error bits in SRR1, in Hardware-

Implementation-Dependent Register 2 (HID2), or in the L2 Cache Control Register (L2CR). A parity error in

either the internal L2 tag array or instruction-cache or data-cache tag arrays is indicated by the CP bit. A data-

parity error on the 60x bus is indicated by the DP bit. The MCpin bit indicates that the machine-check pin was

activated. The transfer error acknowledge (TEA) bit indicates the machine check was caused by a TEA

response on the 60x bus. An address-parity error on the 60x bus will set the AP bit.

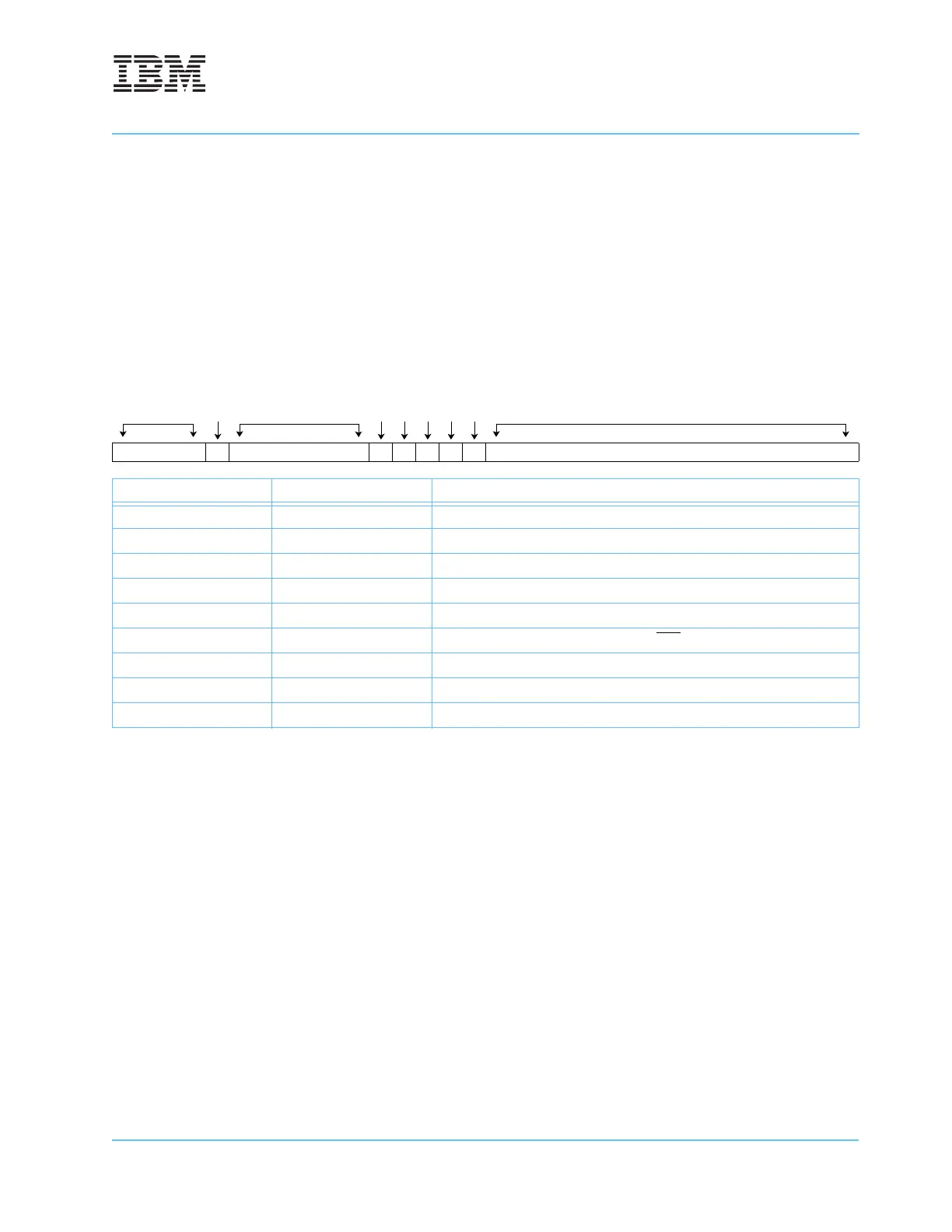

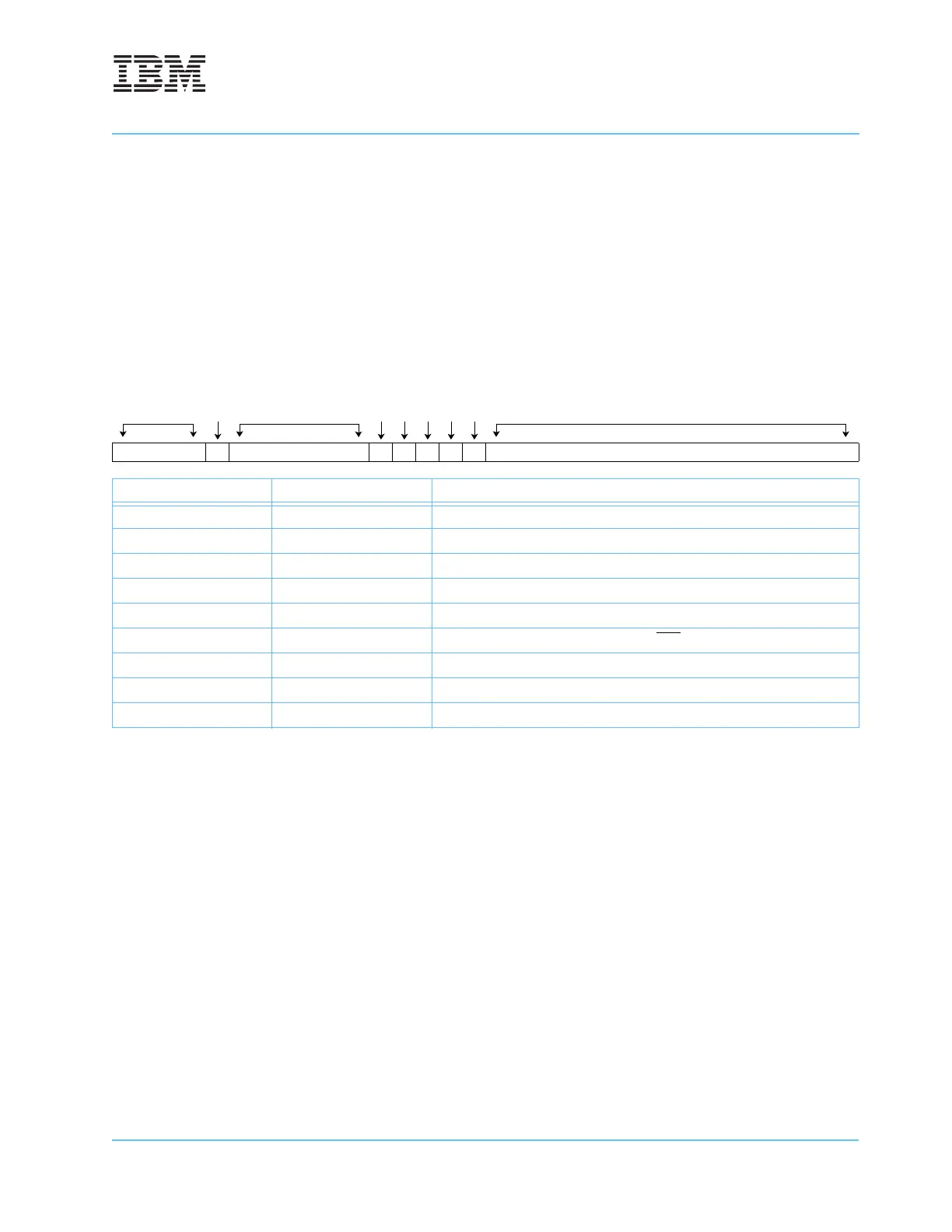

Reserved CP Reserved

L2DBERR

MCpin

TEA

DP AP Reserved

012345678910111213141516171819202122232425262728293031

Bits Field Name Description

0:3 Reserved

4 CP Set when an internal cache parity error is detected.

5:10 Reserved

11 L2DBERR Set when an L2 data-cache ECC double-bit error is detected.

12 MCpin Set when the machine-check pin is asserted.

13 TEA Set when a transfer error acknowledge (TEA

) error is detected.

14 DP Set when a data-bus parity error is detected.

15 AP Set when an address-bus parity error is detected.

16:31 Reserved

Loading...

Loading...