User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_07.fm.(1.2)

March 27, 2006

Signal Descriptions

Page 257 of 377

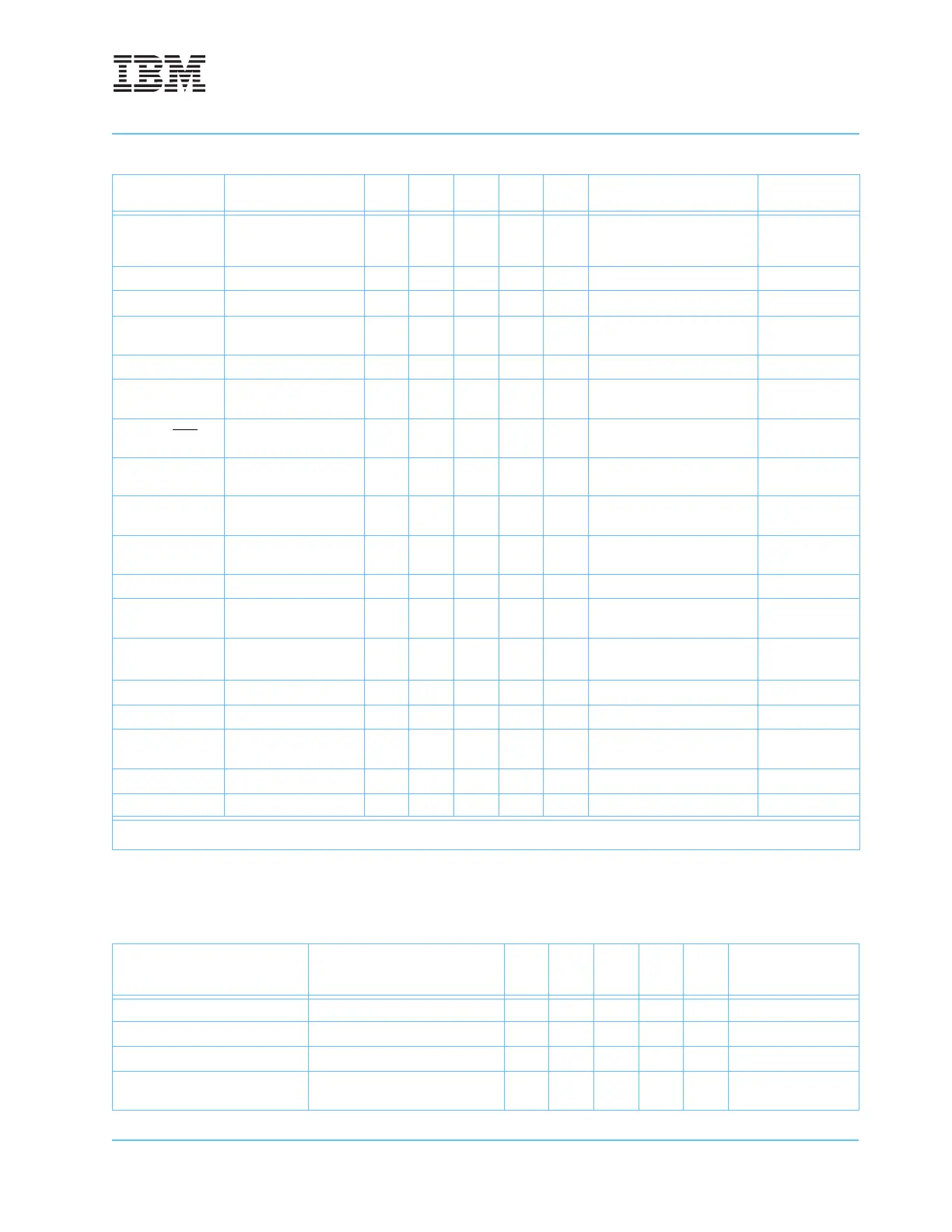

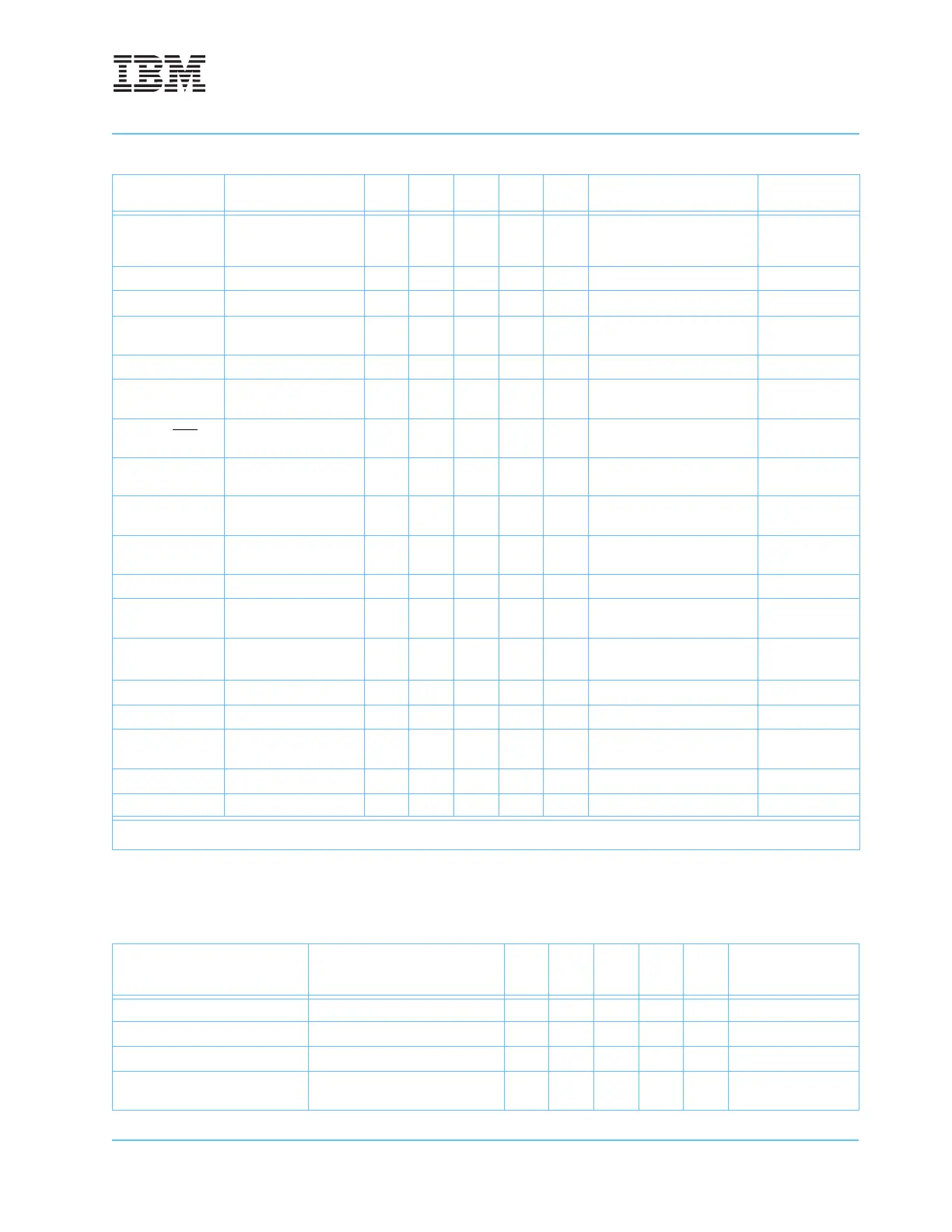

Table 7-2 describes the 60x bus specification transfer encodings and the 750GX bus snoop response on an

address hit.

N/A N/A 00001

Load Word And Reserve

Indexed (lwarx)

reservation set

Address only

N/A N/A 00101Reserved —

N/A N/A 01001TLB Synchronize (tlbsync) Address only

N/A N/A 01101

Instruction Cache Block Inval-

idate (icbi)

Address only

N/A N/A 1 X X 0 1 Reserved —

Single-beat write

Caching-inhibited or

write-through store

00010Write-with-flush

Single-beat write

or burst

Burst (nonGBL

)

Castout, or snoop copy-

back

00110Write-with-kill Burst

Single-beat read

Caching-inhibited load

or instruction fetch

01010Read

Single-beat read

or burst

Burst

Load miss, store miss,

or instruction fetch

01110Read-with-intent-to-modify Burst

Single-beat write

Store Word Conditional

Indexed (stwcx.)

10010Write-with-flush-atomic Single-beat write

N/A N/A 10110Reserved N/A

Single-beat read

lwarx (caching-inhib-

ited load)

11010Read-atomic

Single-beat read

or burst

Burst

lwarx

(load miss)

11110

Read-with-intent-to-modify-

atomic

Burst

N/A N/A 00011Reserved —

N/A N/A 00111Reserved —

N/A N/A 01011Read-with-no-intent-to-cache

Single-beat read

or burst

N/A N/A 01111Reserved —

N/A N/A 1 X X 1 1 Reserved —

Table 7-2. PowerPC 750GX Snoop Hit Response (Page 1 of 2)

60x Bus Specification Command Transaction TT0 TT1 TT2 TT3 TT4

PowerPC 750GX Bus

Snooper;

Action on Hit

Clean block Address only 0 0 0 0 0 N/A

Flush block Address only 0 0 1 0 0 N/A

sync Address only 0 1 0 0 0 N/A

Kill block Address only 0 1 1 0 0

Flush, cancel reserva-

tion

Table 7-1. Transfer Type Encodings for PowerPC 750GX Bus Master (Page 2 of 2)

750GX Bus

Master Transaction

Transaction Source TT0 TT1 TT2 TT3 TT4

60x Bus Specification

Command

Transaction

1. Address-only transaction occurs if enabled by setting the HID0[ABE] bit to 1.

Loading...

Loading...