User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Instruction Timing

Page 234 of 377

gx_06.fm.(1.2)

March 27, 2006

6.4.7 Integer Store Gathering

The 750GX performs store gathering for write-through operations to nonguarded space. It performs cache-

inhibited stores to nonguarded space for 4-byte, word-aligned stores. These stores are combined in the LSU

to form a double word and are sent out on the 60x bus as a single-beat operation. However, stores are gath-

ered only if the successive stores meet the criteria and are queued and pending. Store gathering occurs

regardless of the address order of the stores. Store gathering is enabled by setting HID0[SGE]. Stores can be

gathered in both endian modes.

Store gathering is not done for:

• Cacheable store operations

• Stores to guarded cache-inhibited or write-through space

• Byte-reverse store operations

• Store Word Conditional Indexed (stwcx.) instructions

• External Control Out Word Indexed (ecowx) instructions

• A store that occurs during a table-search operation

• Floating-point store operations

If store gathering is enabled and the stores do not fall under the above categories, an Enforce In-Order

Execution of I/O (eieio) or Synchronize (sync) instruction must be used to prevent two stores from being

gathered.

6.4.8 System Register Unit Execution Timing

Most instructions executed by the SRU either directly access renamed registers or access or modify

nonrenamed registers. They generally execute in a serial manner. Results from these instructions are not

available to subsequent instructions until the instruction completes and is retired. See Section 6.3.2.7,

Instruction Serialization for more information on serializing instructions executed by the SRU, and see

Table 6-5 on page 238 and Table 6-6 on page 240 for SRU instruction execution timings.

Floating-Point

8 byte

8 Optimal — — —

4 — Good Good Good

< 4 — Poor Poor Poor

4 byte

4 Optimal — — —

< 4 Poor Poor Poor Poor

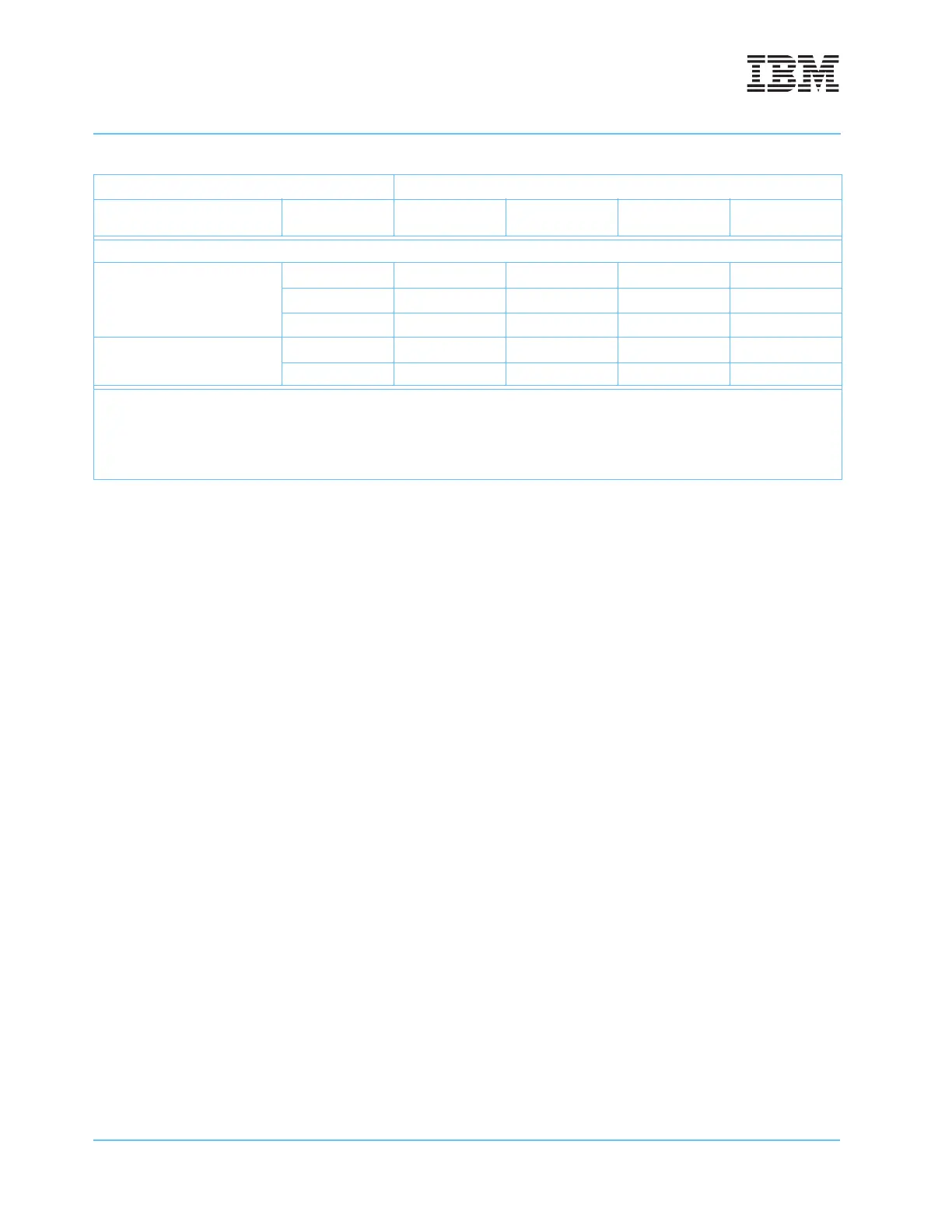

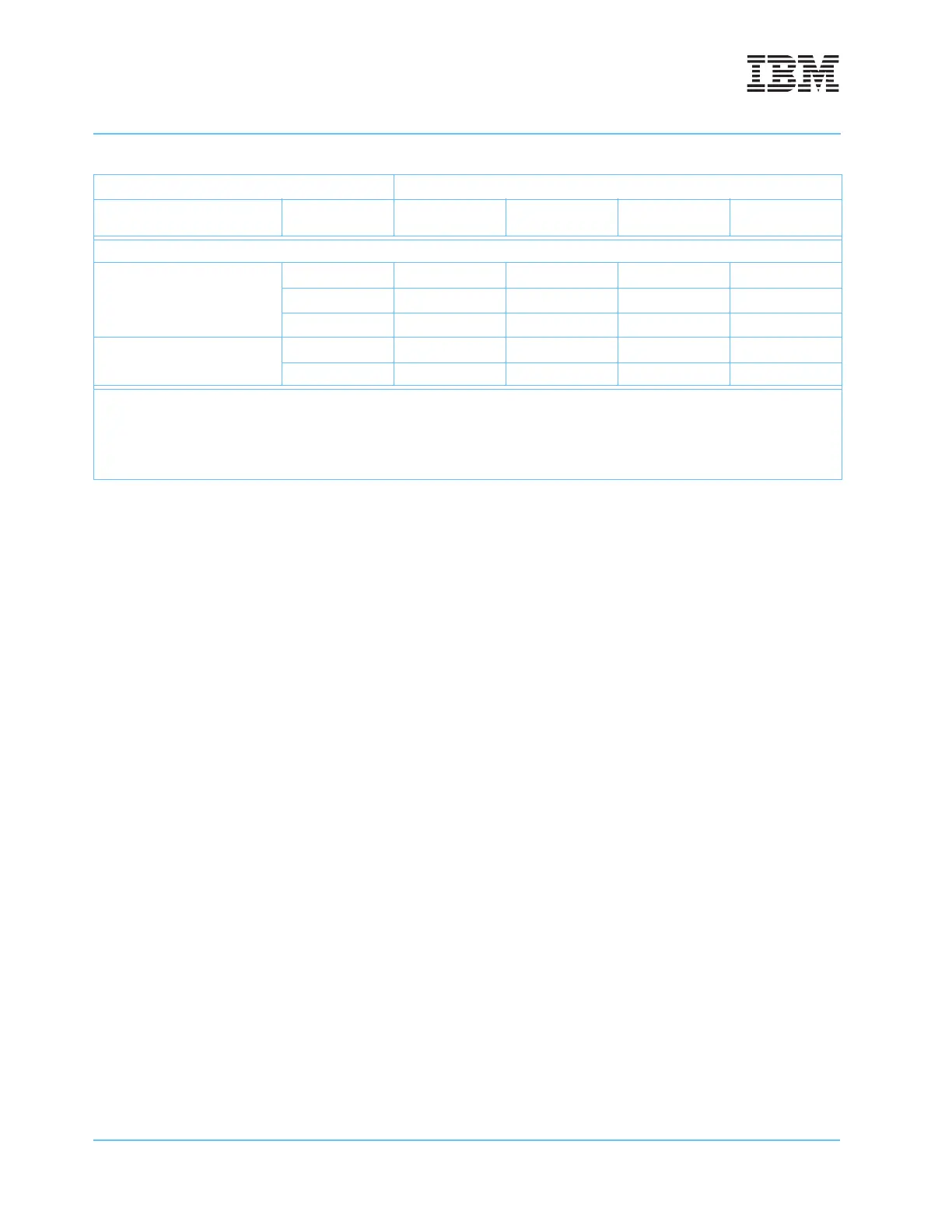

Table 6-2. Performance Effects of Memory Operand Placement (Page 2 of 2)

Operand Boundary Crossing

Size Byte Alignment None 8 Byte Cache Block

Protection

Boundary

Note:

1. Optimal means one EA calculation occurs.

2. Good means multiple EA calculations occur that might cause additional bus activities with multiple bus transfers.

3. Not supported in little-endian mode; causes an alignment exception.

4. Poor means that an alignment exception occurs.

Loading...

Loading...