User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Instruction Timing

Page 212 of 377

gx_06.fm.(1.2)

March 27, 2006

• 64-bit floating-point unit (FPU)

• Load/store unit (LSU)

• System register unit (SRU)

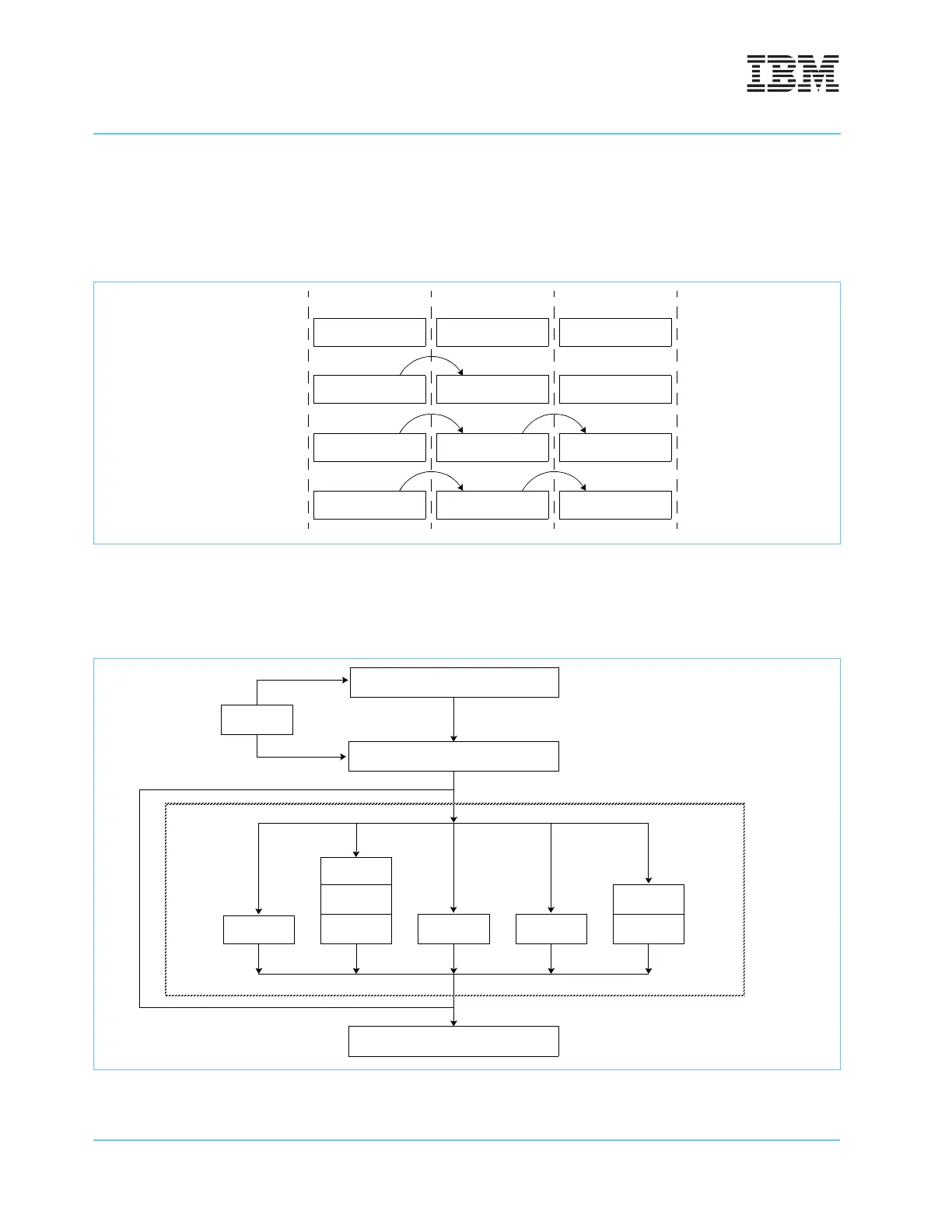

Figure 6-1 represents a generic pipelined execution unit.

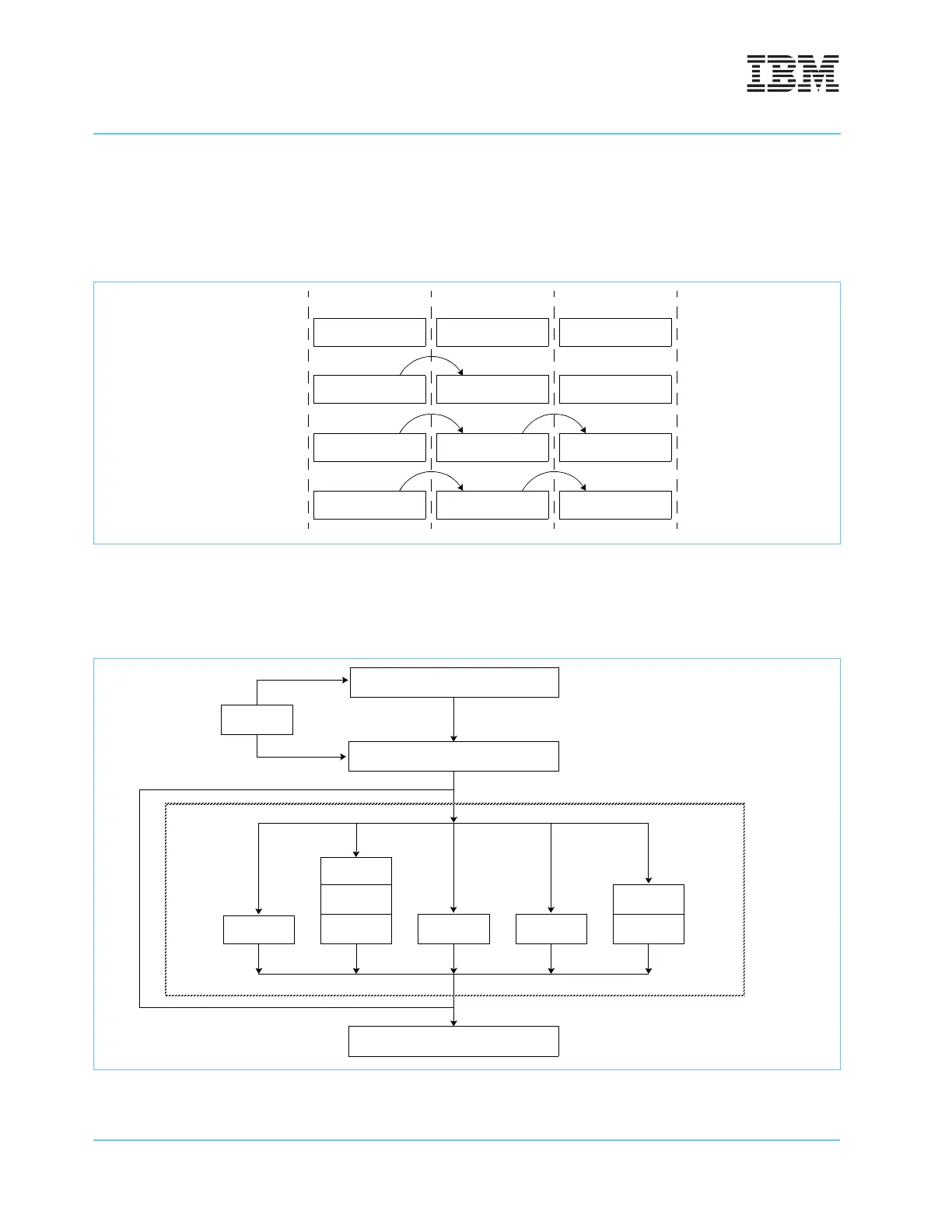

The 750GX can retire two instructions in every clock cycle. In general, the 750GX processes instructions in

four stages—fetch, decode/dispatch, execute, and complete as shown in Figure 6-2. Note that the example of

a pipelined execution unit in Figure 6-1 is similar to the 3-stage FPU pipeline in Figure 6-2.

Figure 6-1. Pipelined Execution Unit

Figure 6-2. Superscalar/Pipeline Diagram

Clock 0

Clock 1

Clock 2

Clock 3

Instruction A — —

Instruction B

Instruction C

Instruction D

Instruction A

Instruction B

Instruction C

—

Instruction A

Instruction B

Fetch

Complete (Write-back)

Decode/Dispatch

Execute Stage

FPU3SRU IU2IU1

Maximum 3-instruction dispatch per

clock cycle (includes one branch

instruction)

Maximum 2-instruction completion per

clock cycle

FPU2

FPU1

LSU1

Maximum 4-instruction fetch per

clock cycle

LSU2

BPU

Loading...

Loading...