User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_06.fm.(1.2)

March 27, 2006

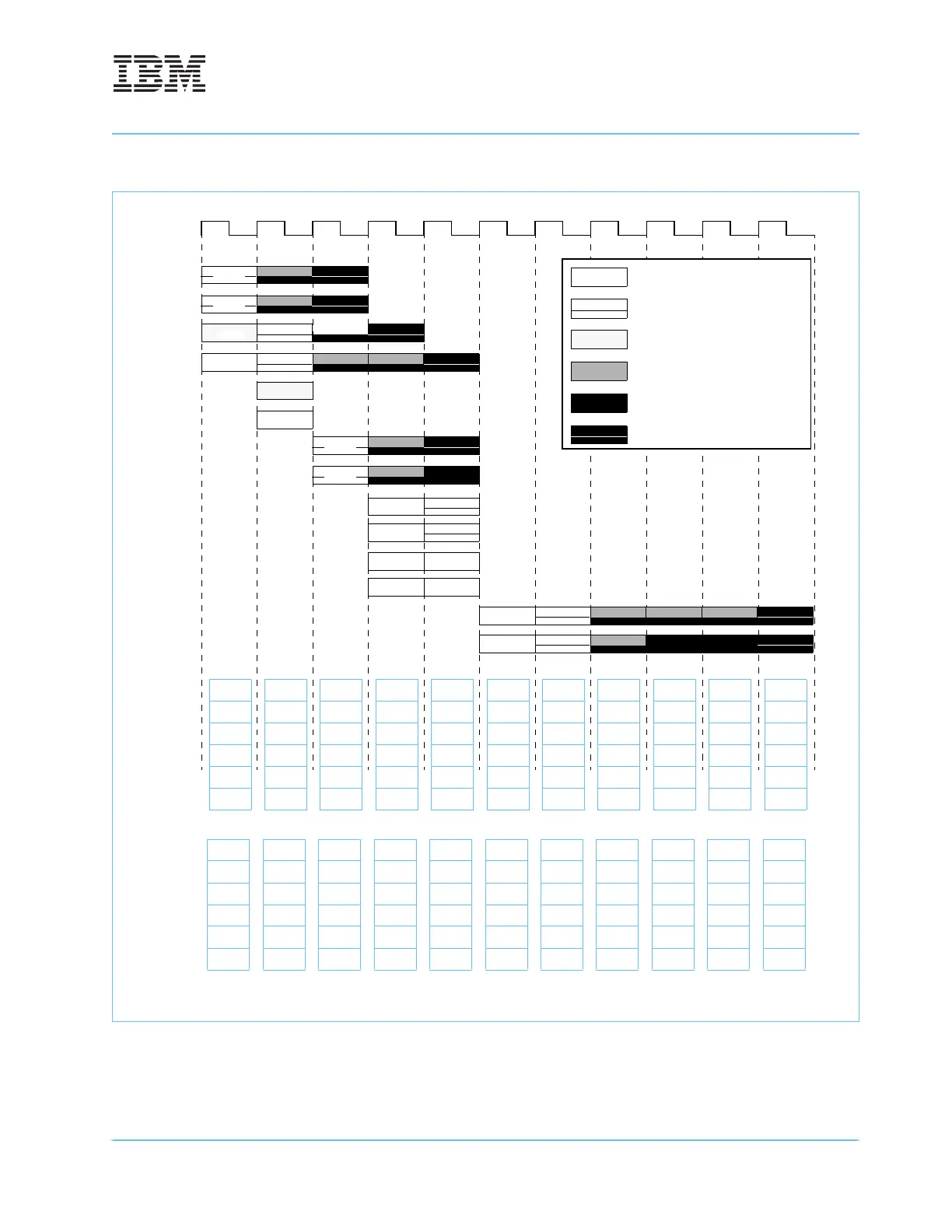

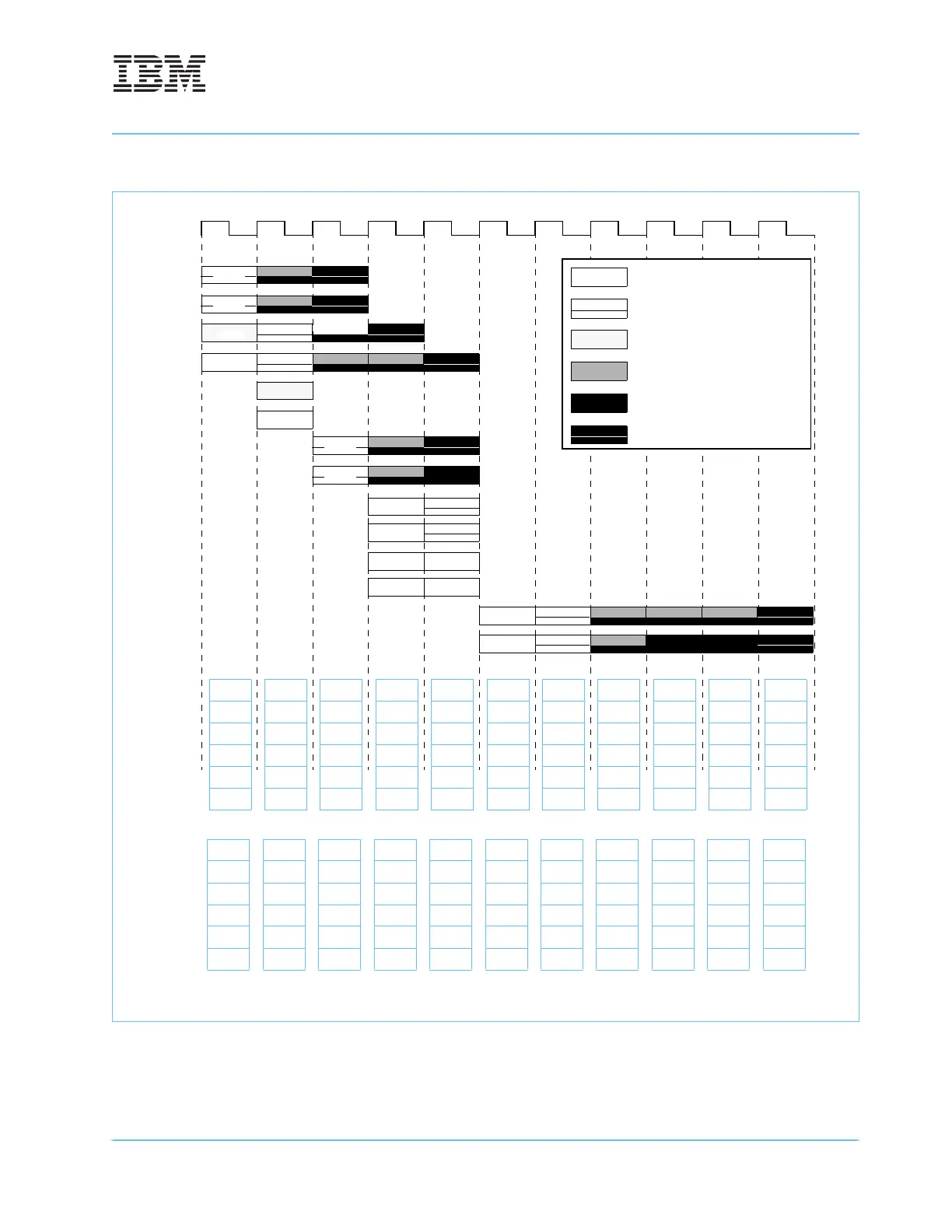

Instruction Timing

Page 231 of 377

1. During clock cycle 0, instructions 0 and 1 are dispatched to their respective execution units. Instruction 2

is a branch instruction that updates the CTR. It is predicted as not taken in clock cycle 0. Instruction 3 is a

Multiply High Word (mulhw) instruction on which instruction 4 depends.

Figure 6-10. Branch Instruction Timing

5 fadd

T3 add

4 bc

123456780 910

•••

•••

Fetch

In dispatch entry (IQ0/IQ1)

Predict

Execute

Complete (In CQ)

In retirement entry (CQ0/CQ1)

1 add

T2 add

3

2 (bc)

1

0

T1

T0

T5

T4

T3

T2

T5

T4

T3

T2

(8)

(7)

6

5

5

4

3

2

3

2

1

0

T1

T0

3

2

T1

T0

3

6

5

(8)

(7)

6

5

(8)

(7)

6

5

(8)

(7)

6

5

1

0

Instruction

Queue

Completion

Queue

0 add

T1 add

T0 add

2 bc

3 mulhw

T5 or

T4 and

5 fadd *

6 and*

* Instructions 5 and 6 are not in the IQ in clock cycle 5. Here, the fetch stage shows cache latency.

Loading...

Loading...