User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Instruction-Cache and Data-Cache Operation

Page 146 of 377

gx_03.fm.(1.2)

March 27, 2006

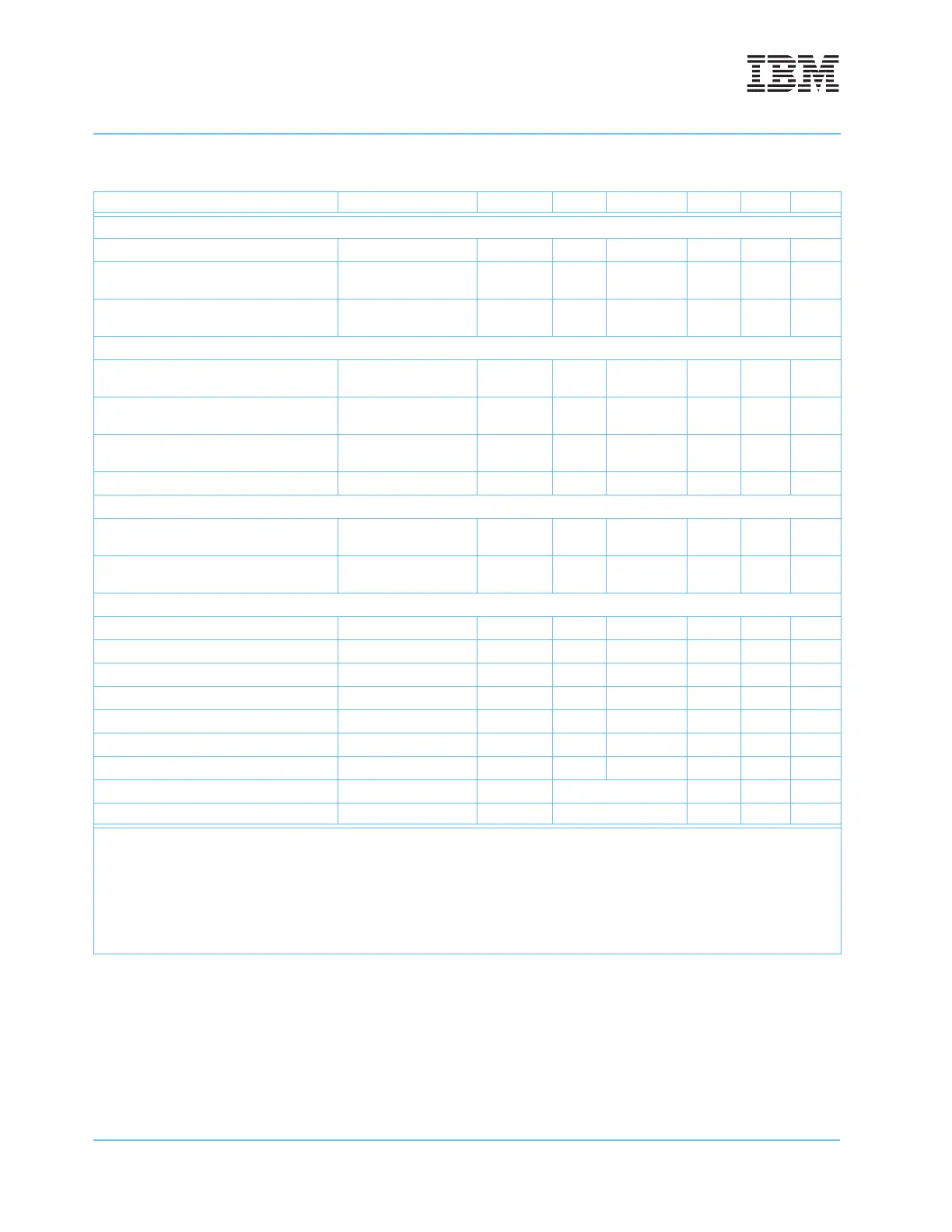

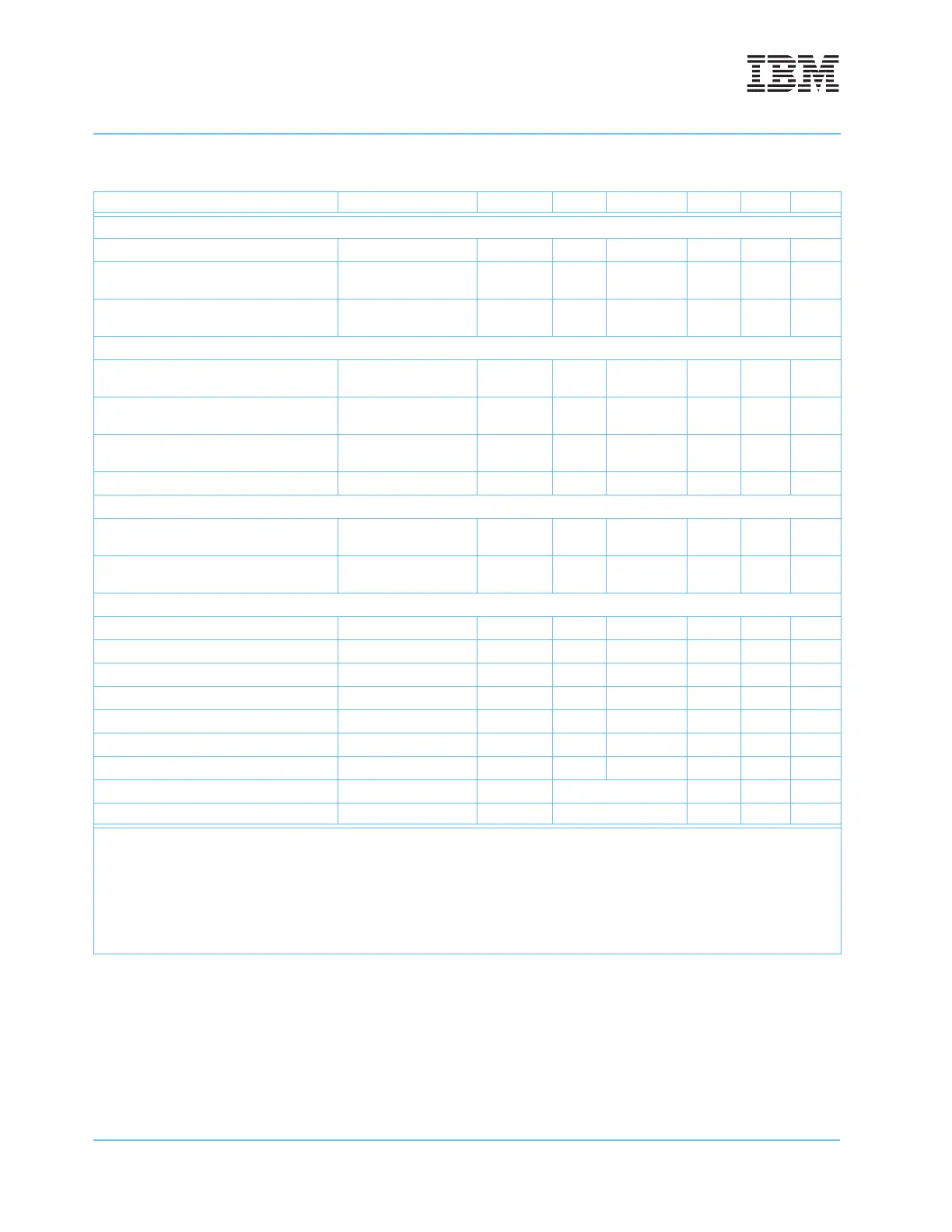

Table 3-6. Address/Transfer Attribute Summary

Bus Transaction A[0–31] TT[0–4] TBST TSIZ[0–2] GBL WT CI

Instruction fetch operations:

Burst (caching-enabled) PA[0–28] || 0b000 0 1 1 1 0 0 0 1 0 ¬ M 1 1*

Single-beat read (caching-inhibited or

cache disabled)

PA[0–28] || 0b000 0 1 0 1 0 1 0 0 0 ¬ M 1 ¬ I

Single-beat read (caching-inhibited or

cache disabled, 32-bit bus)

PA(0:29) || 00 0 1 0 1 0 1 1 0 0 ¬ M 1 ¬ I

Data-cache operations:

Cache-block fill (due to load or store

miss)

PA[0–28] || 0b000 A 1 1 1 0 0 0 1 0 ¬ M 0 1*

Castout

(normal replacement)

CA[0–26] || 0b00000 0 0 1 1 0 0 0 1 0 1 1 1*

Push (cache-block push due to dcbf or

dcbst)

PA[0–26] || 0b00000 0 0 1 1 0 0 0 1 0 1 0 1*

Snoop copyback CA[0–26] || 0b00000 0 0 1 1 0 0 0 1 0 1 0 1*

Data-cache bypass operations:

Single-beat read (caching-inhibited or

cache disabled)

PA[0–31] A 1 0 1 0 1 S S S ¬ M 0 ¬ I

Single-beat write (caching-inhibited,

write-through, or cache disabled)

PA[0–31] 0 0 0 1 0 1 S S S ¬ M ¬W ¬ I

Special instructions:

dcbz (address-only) PA[0–28] || 0b000 0 1 1 0 0 0 0 1 0 0* 0 1*

dcbi (if HID0[ABE] = 1, address-only) PA[0–26] || 0b00000 0 1 1 0 0 0 0 1 0 ¬ M 0 1*

dcbf (if HID0[ABE] = 1, address-only) PA[0–26] || 0b00000 0 0 1 0 0 0 0 1 0 ¬ M 0 1*

dcbst (if HID0[ABE] = 1, address-only) PA[0–26] || 0b00000 0 0 0 0 0 0 0 1 0 ¬ M 0 1*

sync (if HID0[ABE] = 1, address-only) 0x0000_0000 0 1 0 0 0 0 0 1 0 0 0 0

eieio (if HID0[ABE] = 1, address-only) 0x0000_0000 1 0 0 0 0 0 0 1 0 0 0 0

stwcx. (always single-beat write) PA[0–29] || 0b00 1 0 0 1 0 1 1 0 0 ¬ M ¬ W ¬ I

eciwx PA[0–29] || 0b00 1 1 1 0 0 EAR[28–31] 1 0 0

ecowx PA[0–29] || 0b00 1 0 1 0 0 EAR[28–31] 1 1 0

Note:

PA = Physical address, CA = Cache address.

W,I,M = WIM state from address translation; ¬ = complement; 0*or 1* = WIM state implied by transaction type in table

For instruction fetches, reflection of the M bit must be enabled through HID0[IFEM].

A = Atomic; high if lwarx, low otherwise

S = Transfer size

Special instructions listed might not generate bus transactions depending on cache state.

Loading...

Loading...