User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_05.fm.(1.2)

March 27, 2006

Memory Management

Page 187 of 377

When the processor generates an access, and the corresponding address-translation-enable bit in the MSR

is cleared, the resulting physical address is identical to the effective address, and all other translation mecha-

nisms are ignored. Instruction address translation and data address translation are enabled by setting

MSR[IR] and MSR[DR], respectively.

5.1.4 Memory-Protection Facilities

In addition to the translation of effective addresses to physical addresses, the MMUs provide access protec-

tion of supervisor areas from user access and can designate areas of memory as read-only, as well as no-

execute or guarded. Table 5-2 on page 188 shows the protection options supported by the MMUs for pages.

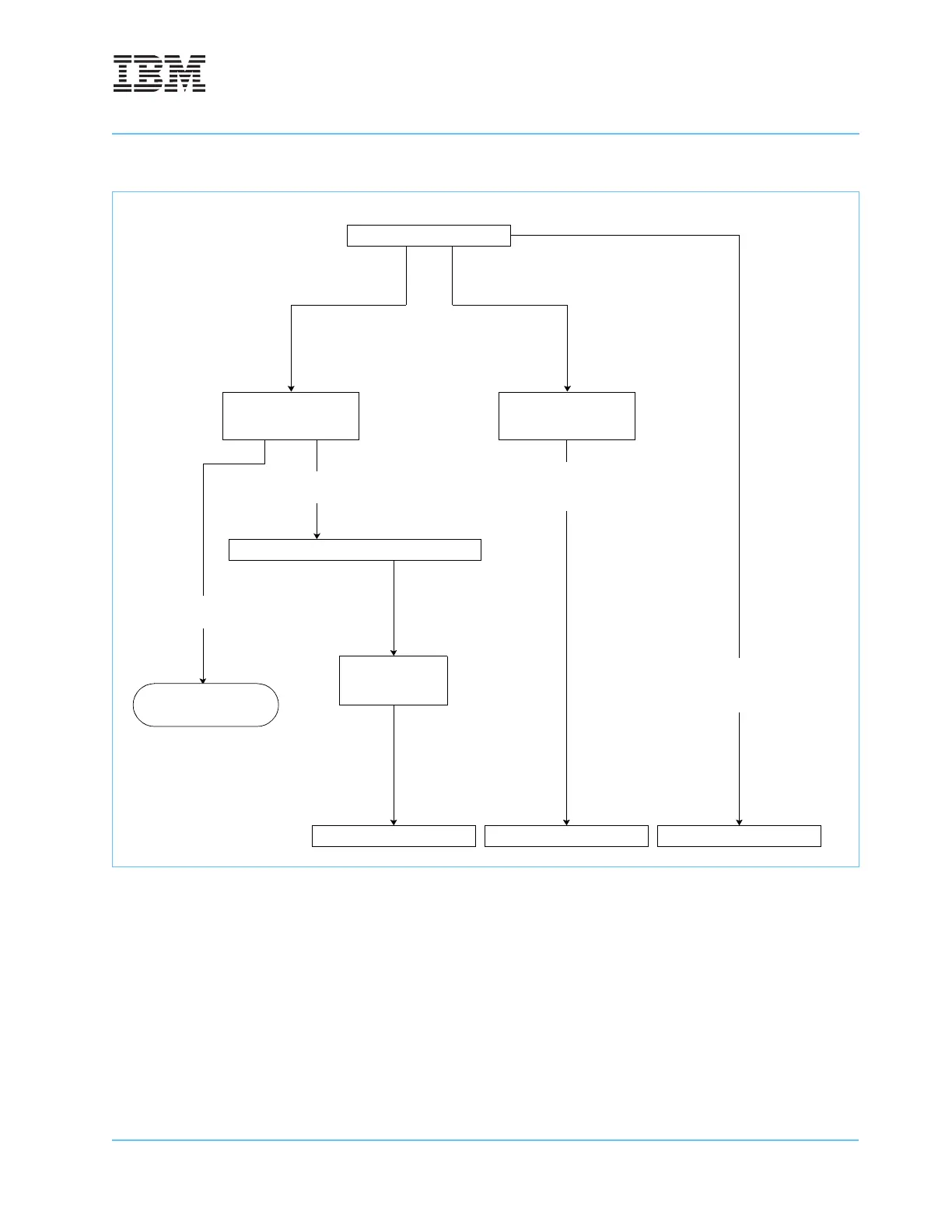

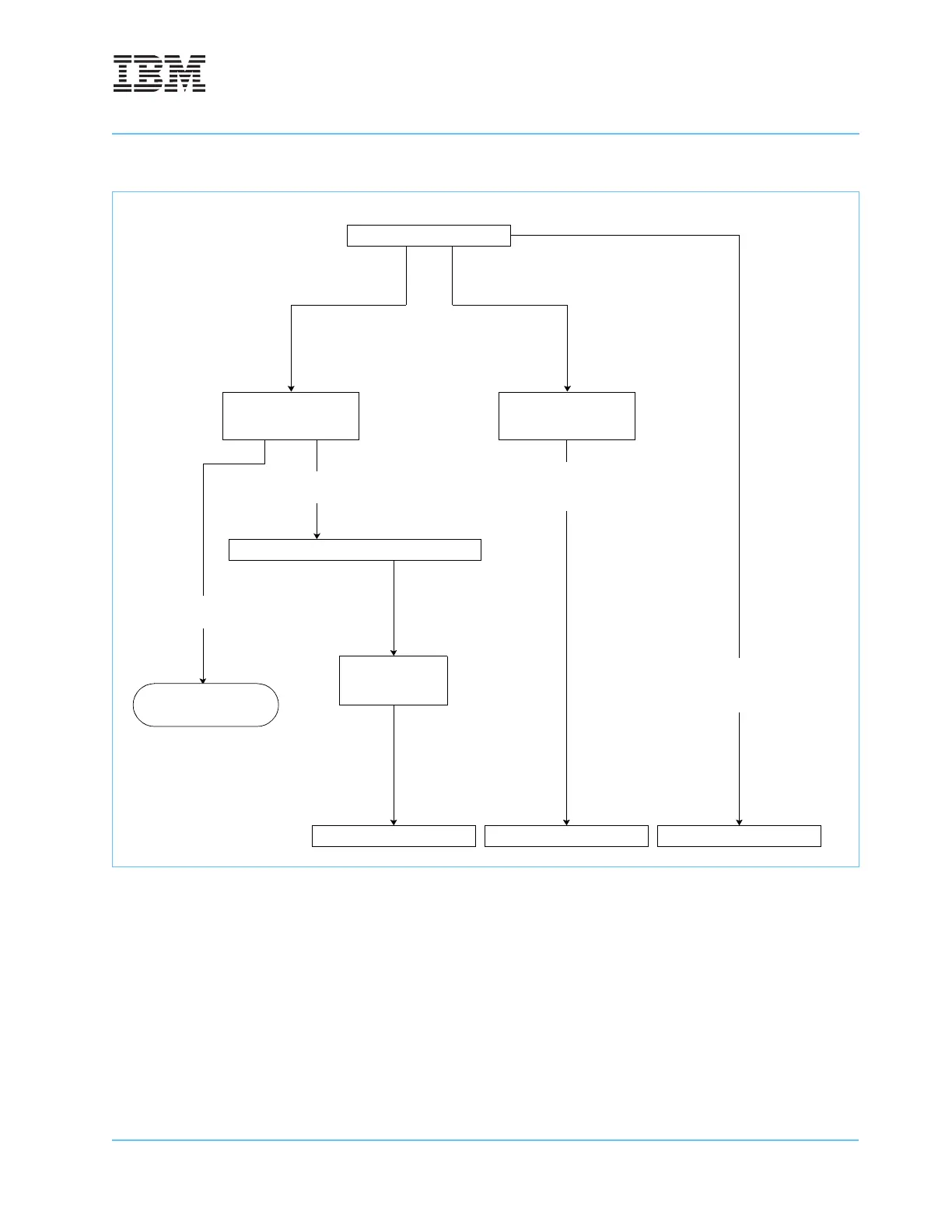

Figure 5-4. Address-Translation Types

(T = 1)

Physical Address

0 31

(T = 0)

0

Effective Address

0

Virtual Address

Segment Descriptor

Located

Match with BAT

Registers

Look Up in

Page Table

Address Translation Disabled

Page Address

Translation

Direct-Store Interface

Translation

(MSR[IR] = 0, or MSR[DR] = 0)

Real Addressing Mode

Effective Address = Physical Address

(See Section 5.2 on page 195)

Block Address Translation

(See Section 5.3 on page 196)

DSI/ISI Exception

0 31 0 31

Physical AddressPhysical Address

Loading...

Loading...